### **SECTION B**

#### NMOS & CMOS inverters and Gates Lamda Base rule.

### **Topic Covered**

- NMOS & CMOS INVERTER AND GATES : NMOS & CMOS inverter – Determination of pull up /

- pull down ratios Stick diagram Lamda based rules – Super buffers – BiCMOS & steering logic

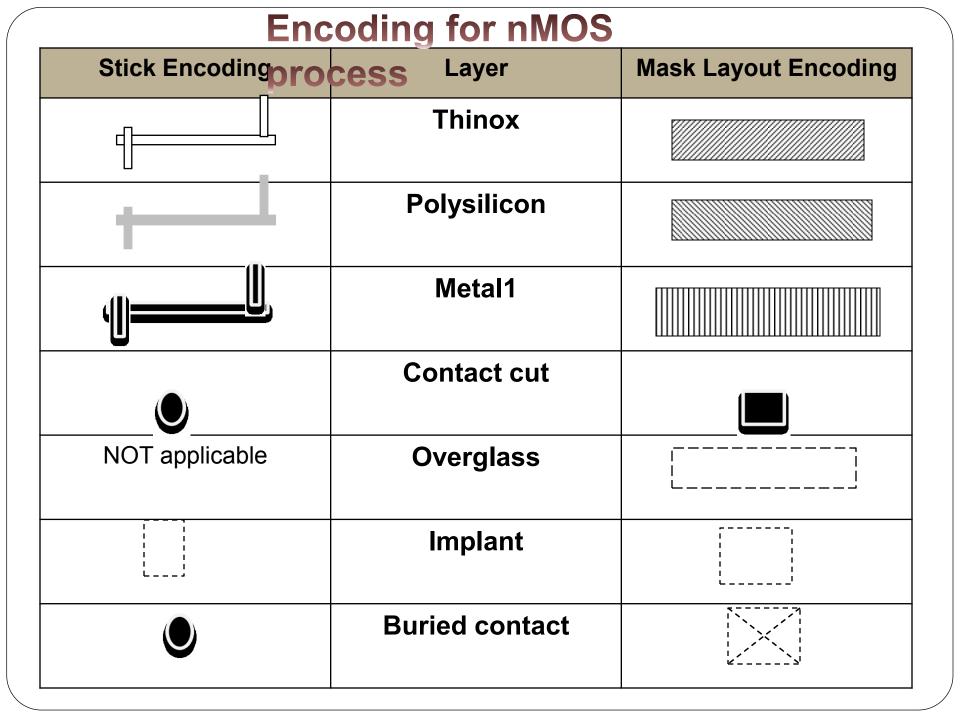

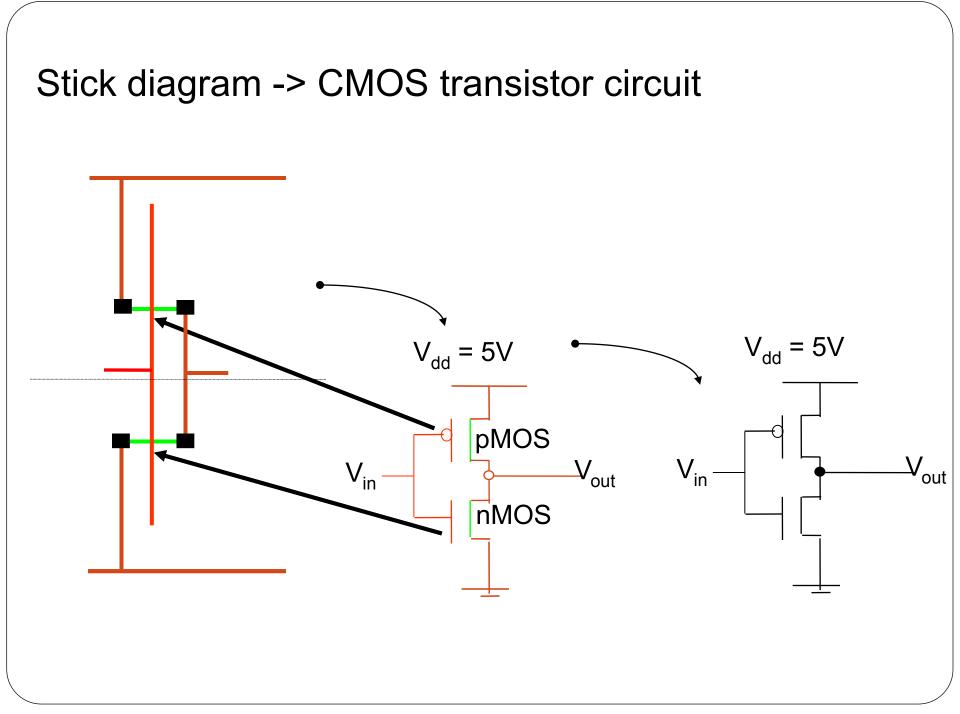

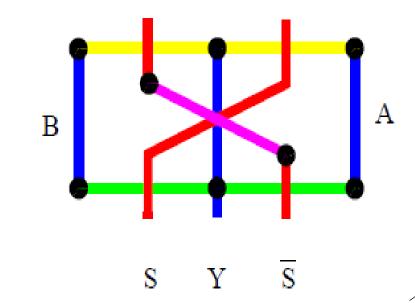

### Stick Diagrams

- VLSI design aims to translate circuit concepts onto silicon

- stick diagrams are a means of capturing topography and layer information - simple diagrams

- Stick diagrams convey layer information through color codes (or monochrome encoding)

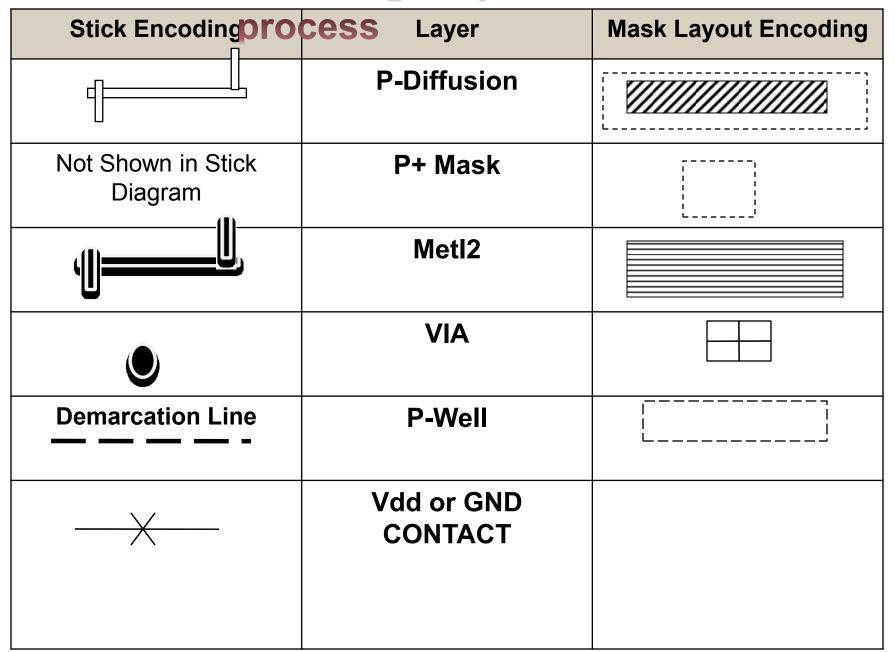

#### **Encoding for pMOS**

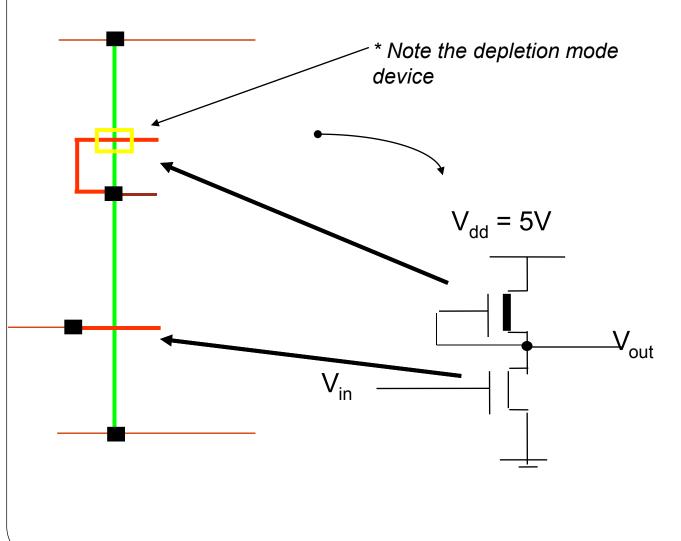

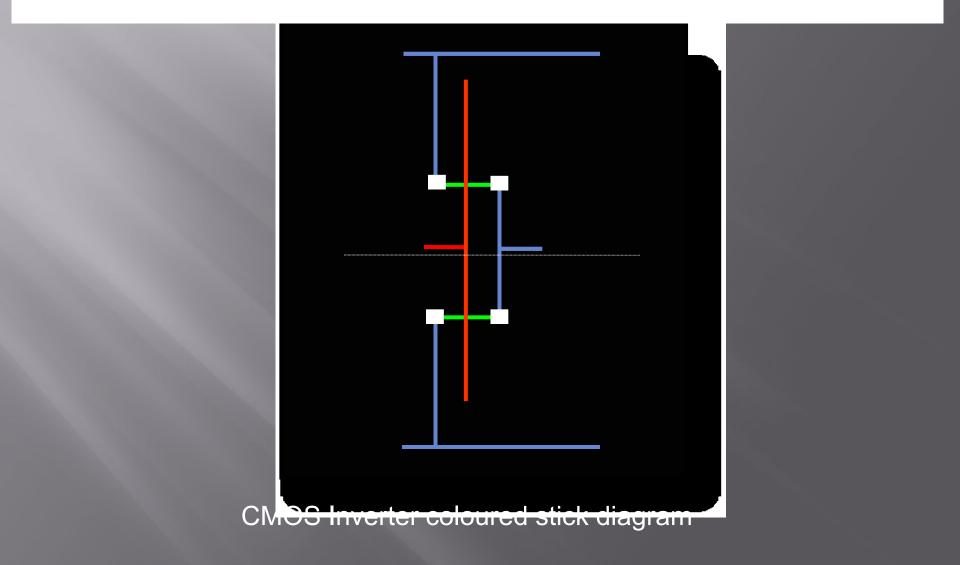

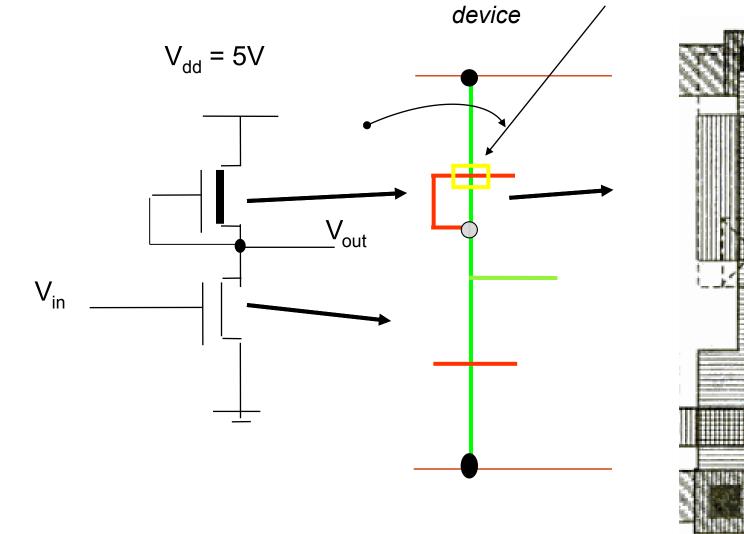

# For reference : an nMOS Inverter coloured stick diagram

# Only metal and polysilicon can cross the dimarcation line.

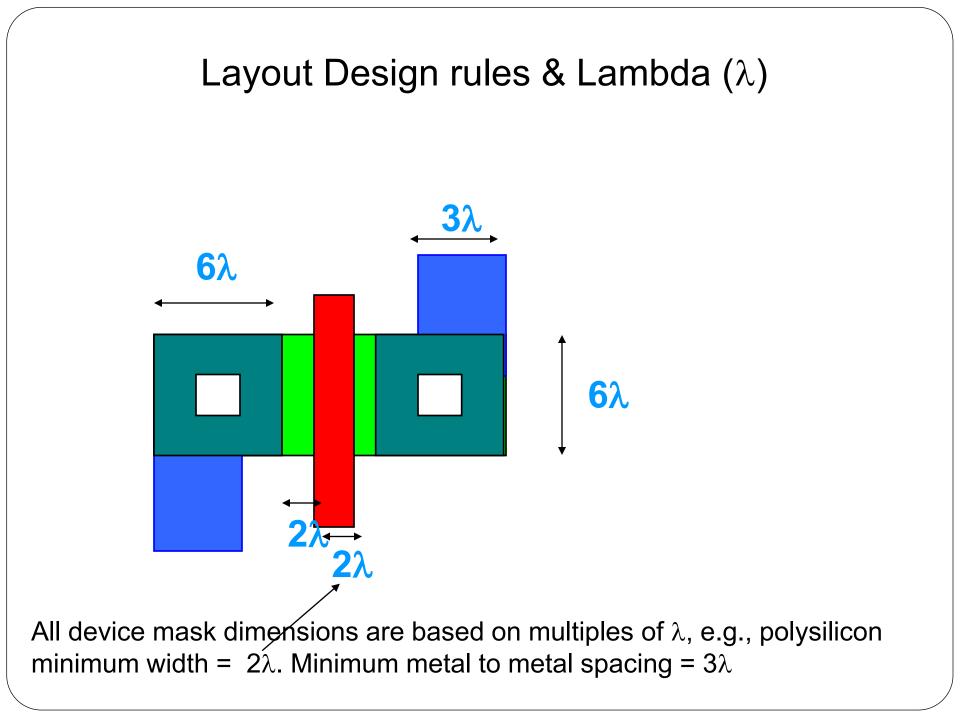

All paths in all layers will be dimensioned in  $\lambda$  units and subsequently  $\lambda$  can be allocated an appropriate value compatible with the feature size of the fabrication process.

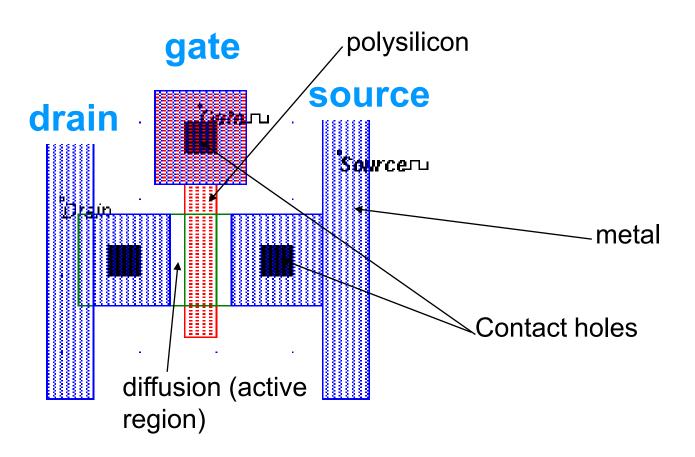

#### nMOS transistor mask representation

### **Contact Cuts**

- Three possible approaches –

- 1. Poly to Metal

- 2. Metal to Diffusion

Buried contact (poly to diff) or butting contact (poly to diff using metal)

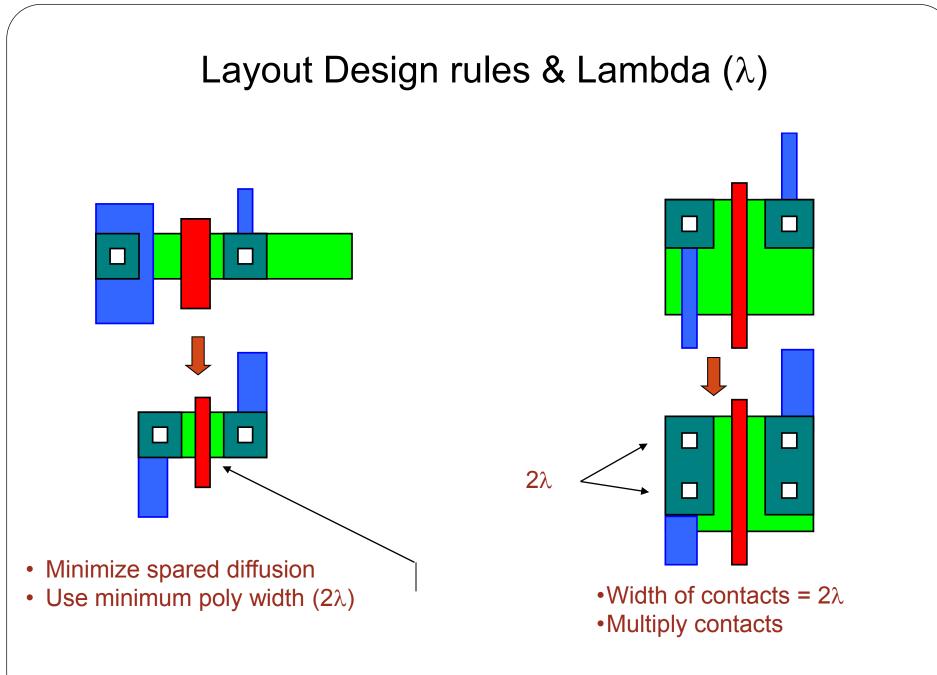

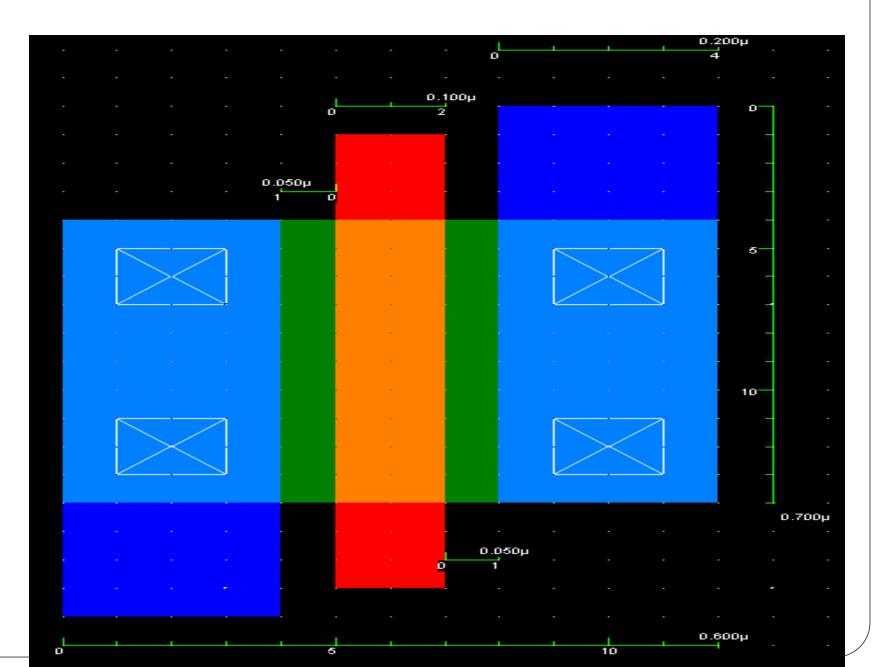

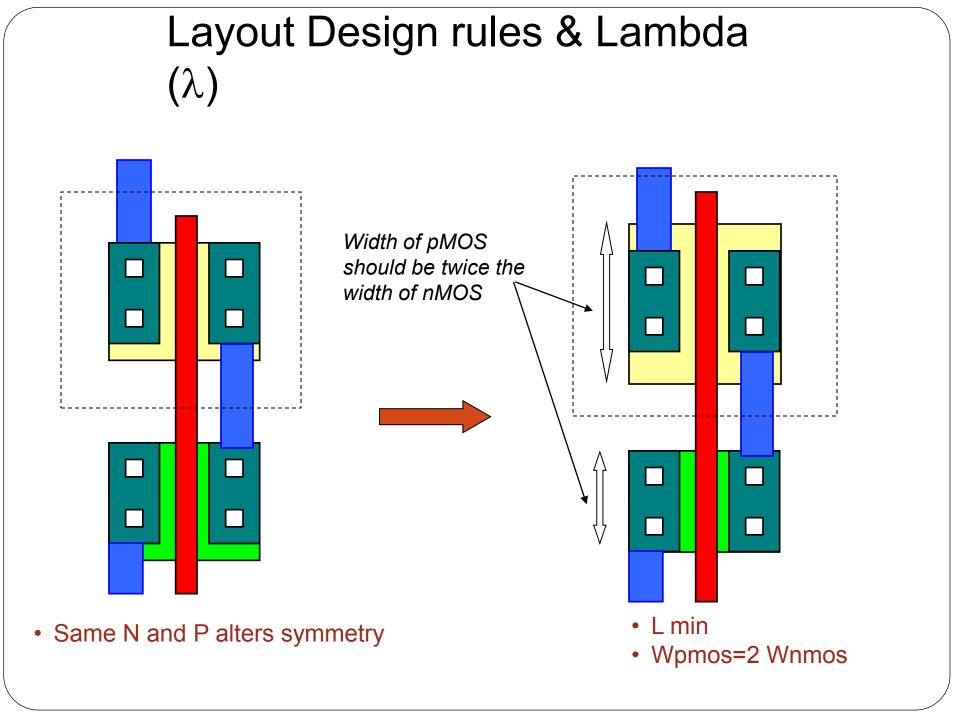

### Layout Design rules & Lambda ( $\lambda$ )

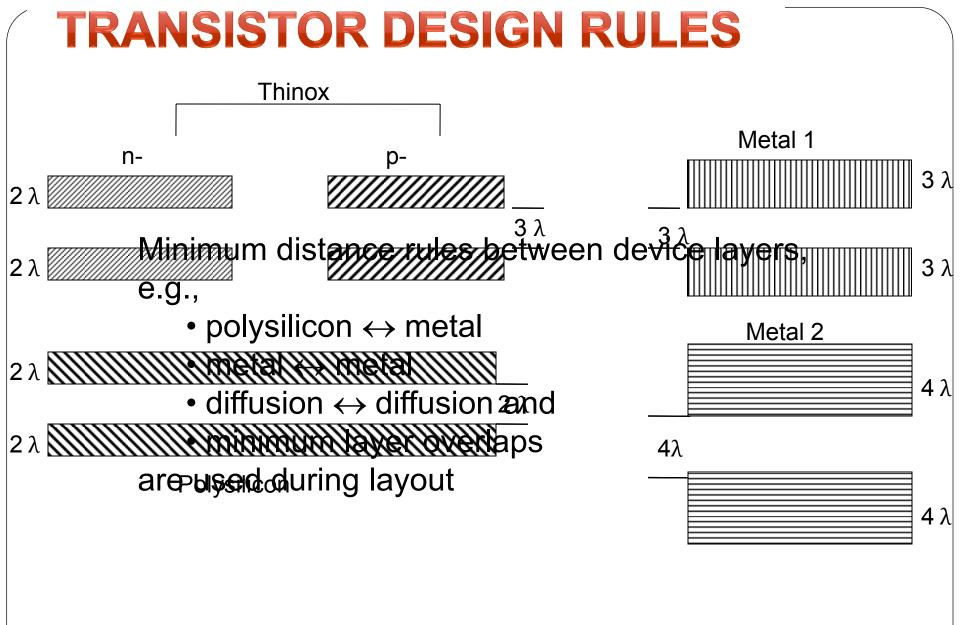

### Lambda Based Design Rules

- Design rules based on single parameter, λ

- Simple for the designer

- Wide acceptance

- Provide feature size independent way of setting out mask

- Minimum feature size is defined as 2  $\lambda$

- Used to preserve topological features on a chip

- Prevents shorting, opens, contacts from slipping out of area to be contacted

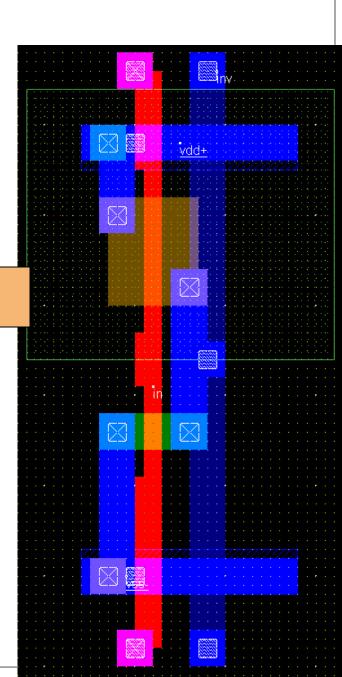

#### \*\*\* ..... inv X 🐟 Palette vdd+ $\boxtimes$ Ρ -8 Ν while while $\boxtimes$ 🔹 🔹 🥻 ጠ ቢ 🗸 🔹 Options Х Metal 6 Metal 5 Metal 4 Metal 3 Metal 2 ☑ Metal 1 ☑ $\boxtimes$ $\boxtimes$ Polysilicon 2 Contact Polysilicon P+ Diffusion N+ Diffusion N Well VSS Clock1 ىر: 🔤

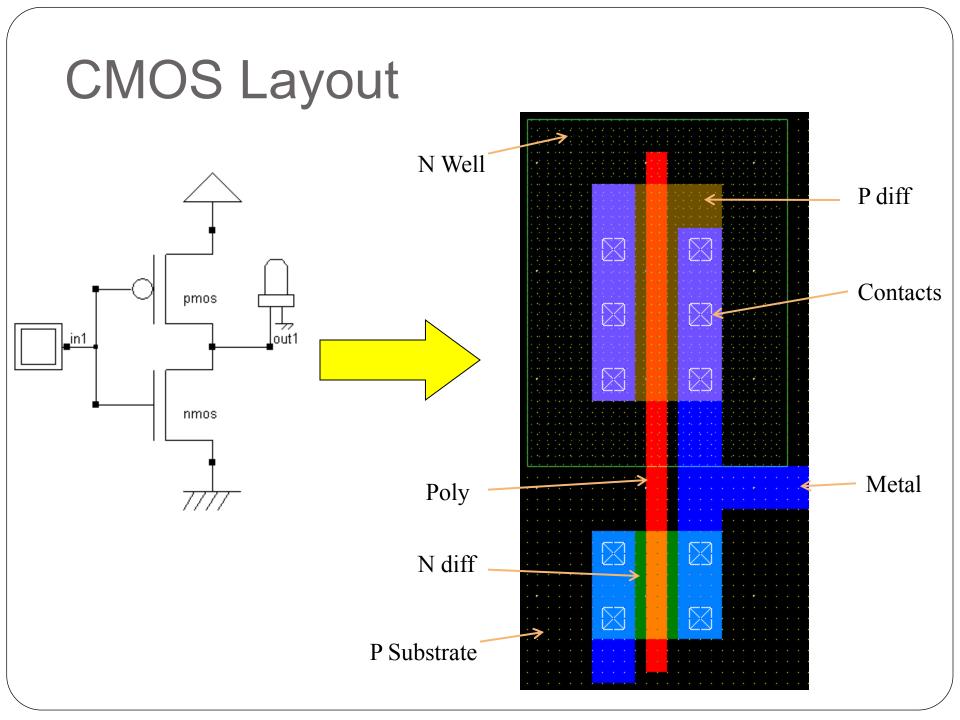

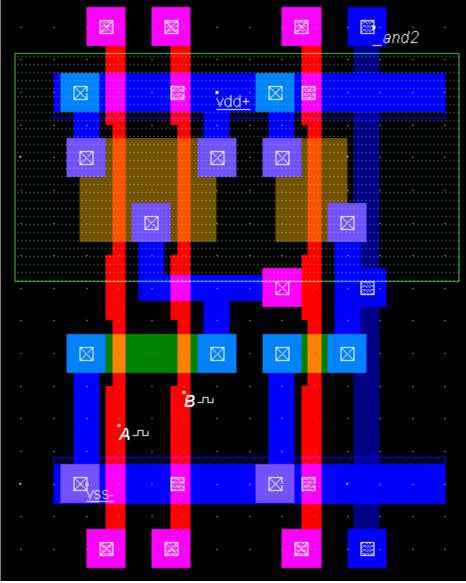

#### CMOS Inverter Mask Lavout

## MOS Layout Design

- CMOS IC are designing using stick diagrams.

- Different color codes for each layer.

- Lamda/micron grid.

#### CMOS AN2 (2 i/p AND gate) Mask Layout

#### nMOS Inverter coloured stick diagram

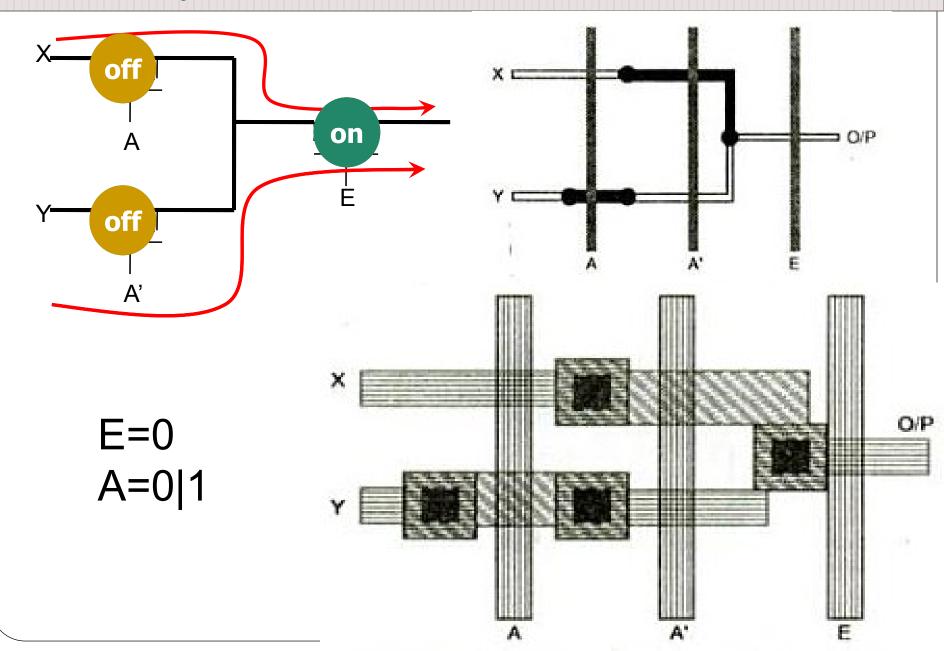

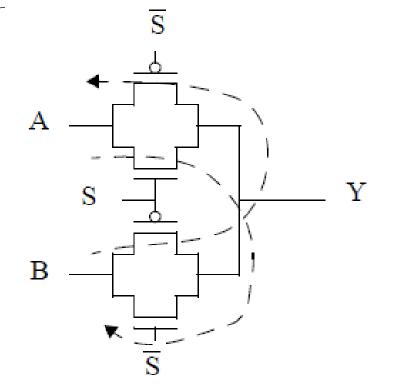

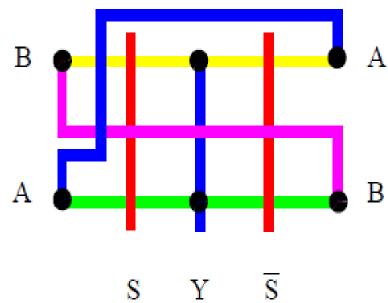

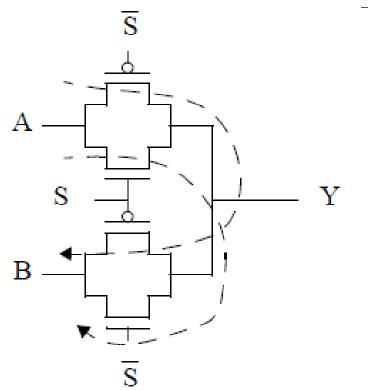

### Two-way selector with enable

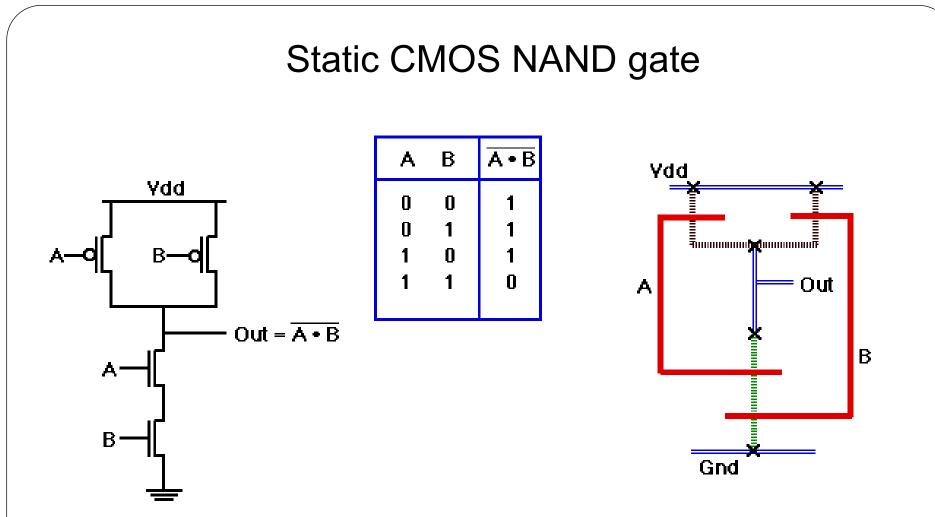

1. Pull-down: Connect to ground If A=1 AND B=1

2. Pull-up: Connect to Ydd If A=0 OR B=0

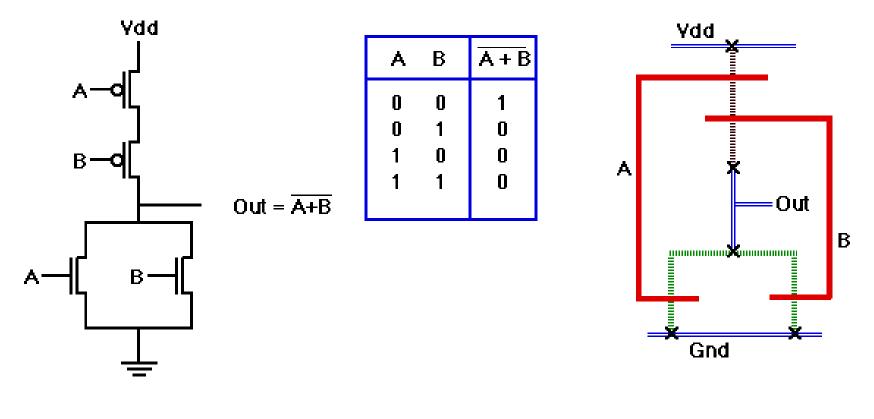

#### Static CMOS NOR gate

1. Pull-down: Connect to ground If A=1 OR B=1

2. Pull-up: Connect to Ydd If A=0 AND B=0

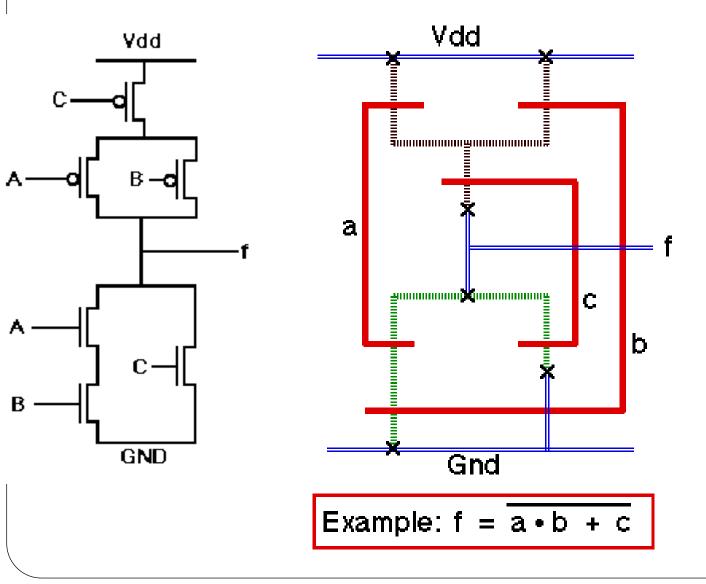

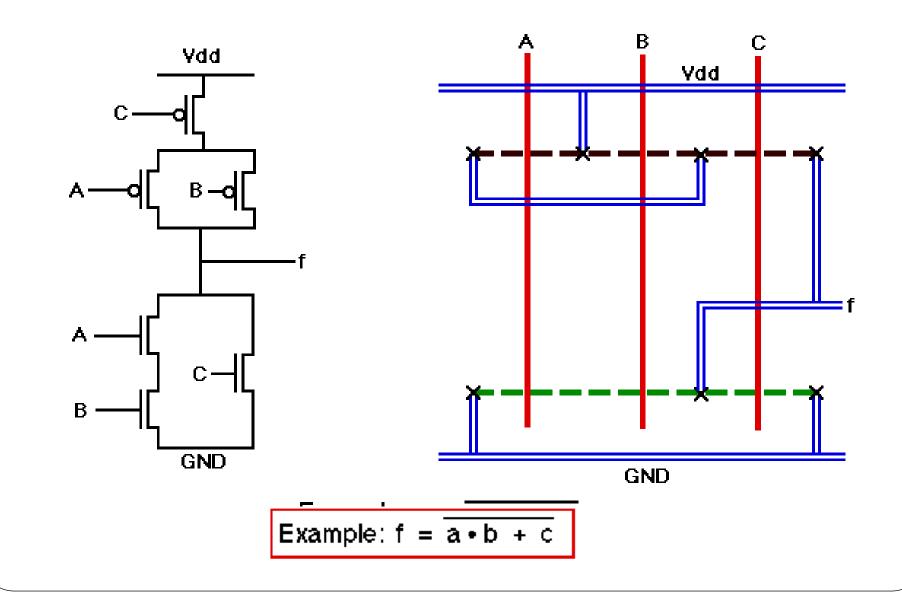

#### Static CMOS Design Example Layout

Layout 2 (Different layout style to previous but same function being implemented)

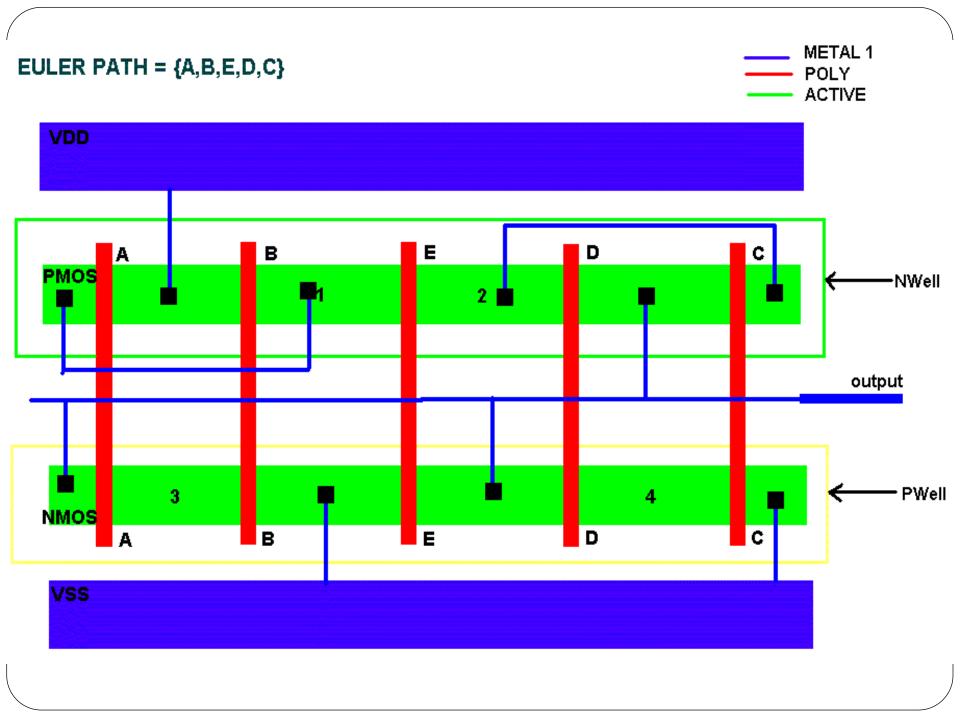

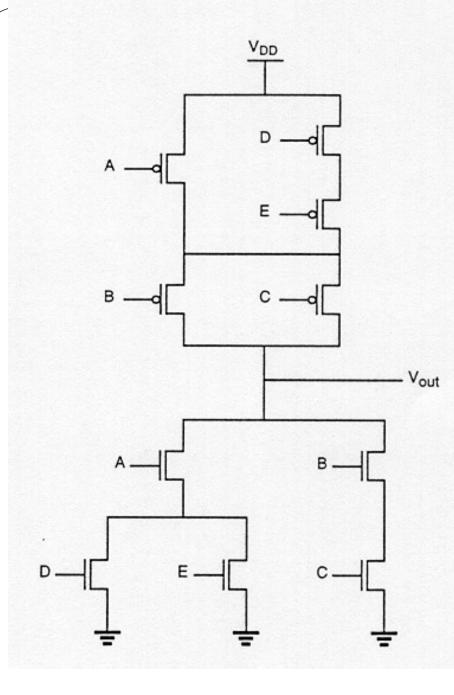

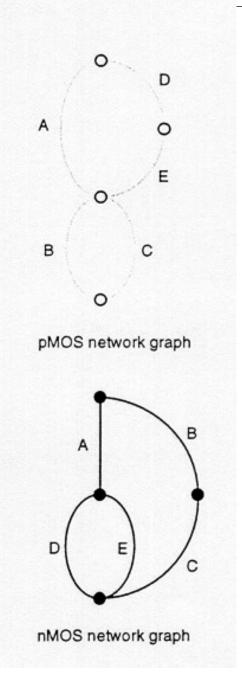

### Complex logic gates layout

- Ex—<del>F=AB+E+</del>CD

- Eulerpaths

- Circuit to graph (convert)

- 1) Vertices are source/Drain connections

- 2) Edges are transistors

- Find p and n Eulerpaths

А в А в Е Е 2 ¥2 D С D С output output А D Ø А Е з 4 З Е в С в С vss PDN vss PDN EULER PATH = {A,B,E,D,C}

F = (AB)+E+(CD)

PUP

VDD

PUP

VDD

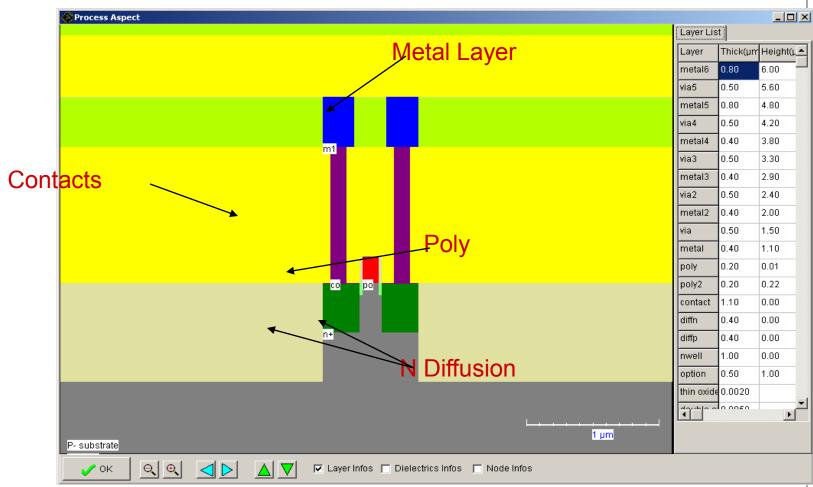

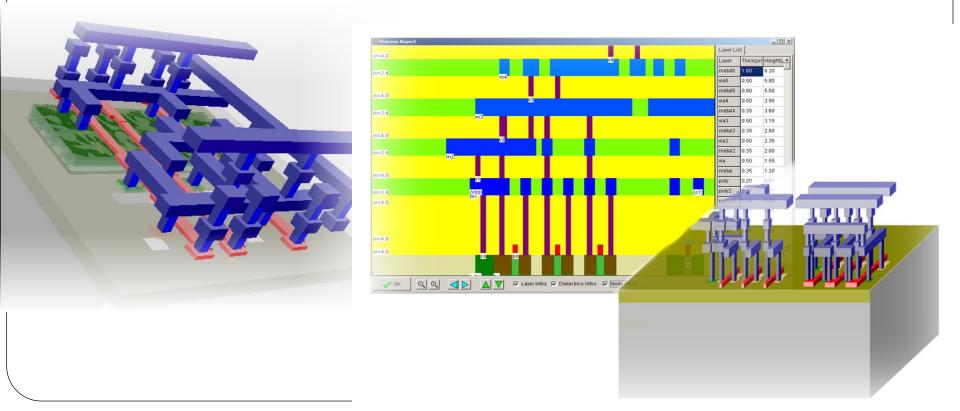

### VirtuosoFab

Touch the deep submicron technology

- 3D fabrication process simulator with cross sectional viewer.

- Step-by-step 3-D visualization of fabrication for any portion of layout.

#### 2D Cross Section NMOS Transistor