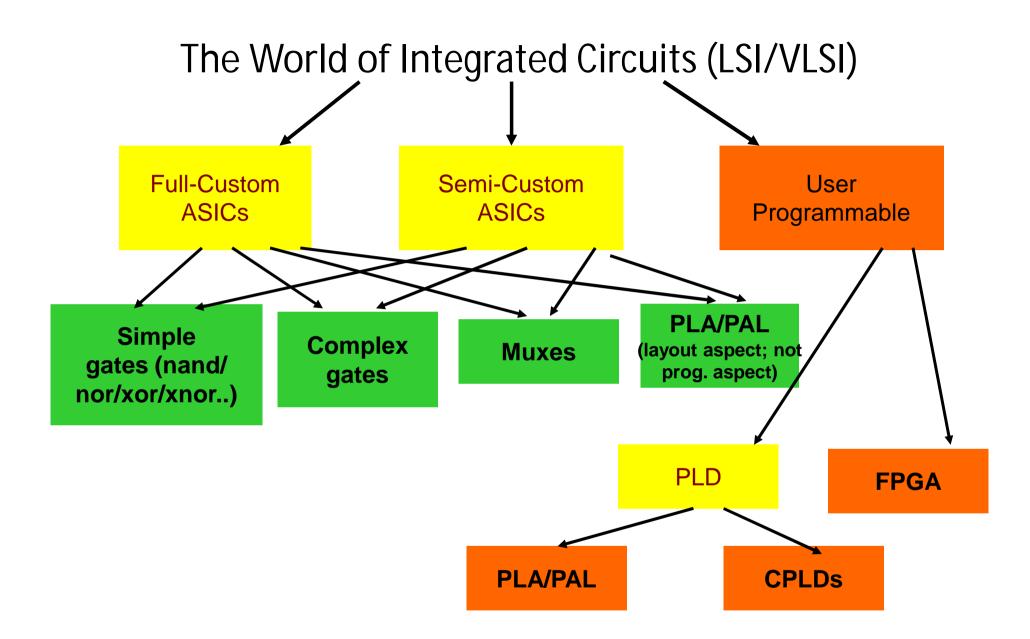

#### Logic Design Using Multiplexers

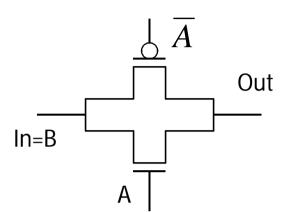

A Transmission Gate (T-Gate)

Steering gate.

When A=1, 'In' is "Steered" to 'Out'. [I.e., the T-gate conducts] Thus Out = B when A=1

Out = AB

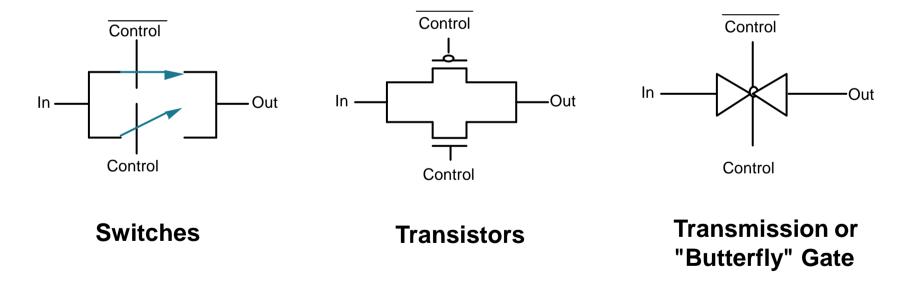

Symbolic for T-gate:

A is the control input (CI) Normal CI connected to A Bubbled CI connected to

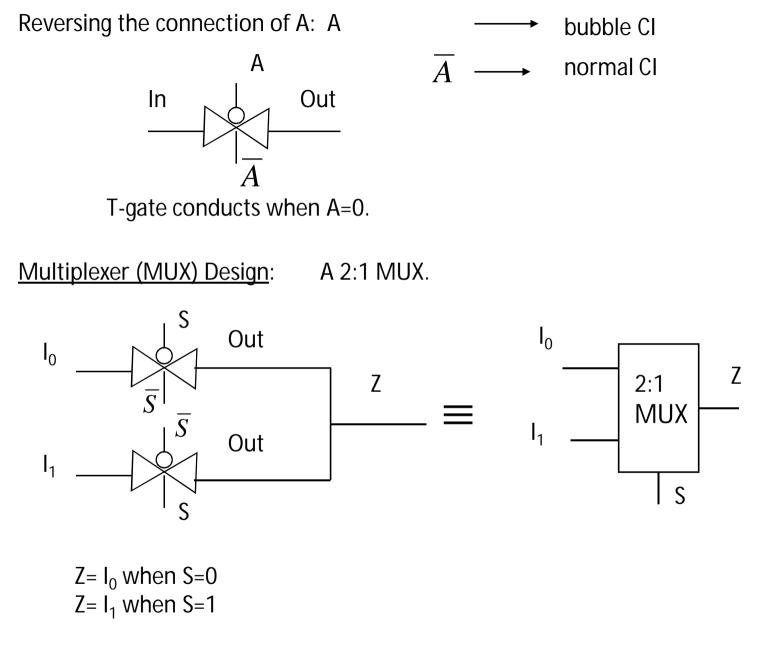

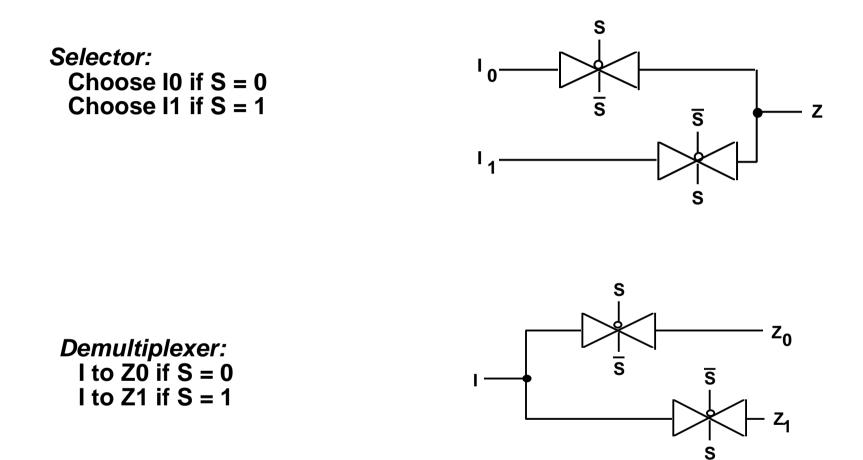

Steering Logic are the circuits that route data inputs to outputs based on the setting of control signals.

- For any combination of the control inputs there must be at least one conducting path from an input to the output. i, e the output node should always be driven from some input.

- There should never be more than one conducting path between the inputs and an output. i.e in that case one path might attempt to drive the output node to logic 1 while another drives to logic 0.

$\Box = \overline{SI}_0 + SI_1$

5

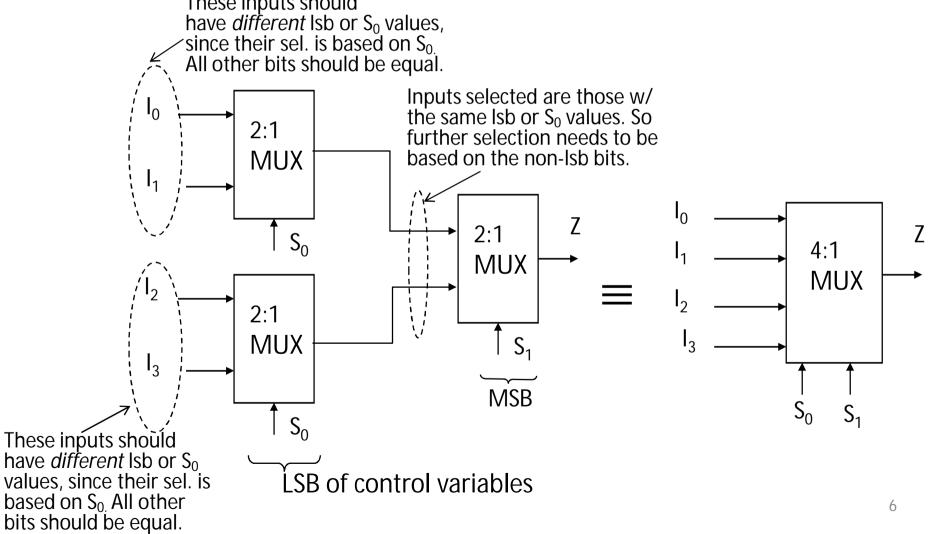

## Design of MUXes using Divide-&-Conquer

- Saw the design of a 2:1 MUX using T-gates, as well as logic gates

- Messy and expensive to design larger MUXes using a flat TT based approach

- A 4:1 MUX can be hierarchically constructed using 2:1 MUXes

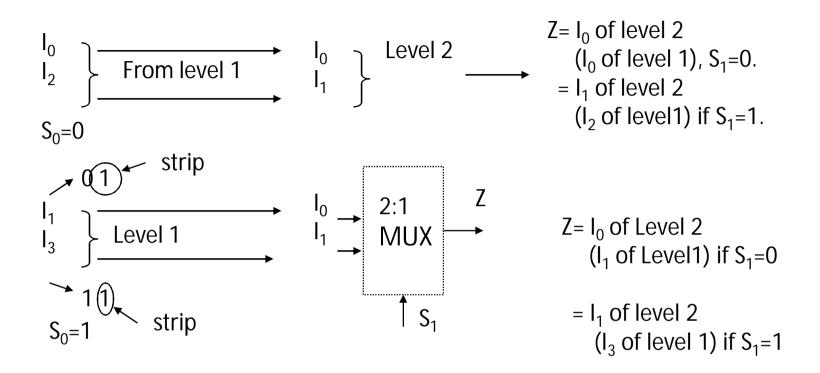

- Idea: Divide the selection problem by bits of the select/control variables These inputs should

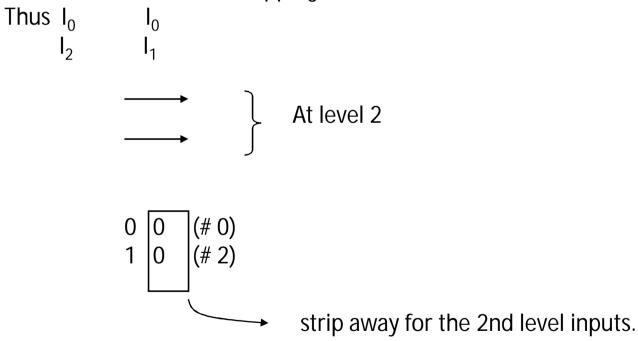

When  $S_0=0$ ,  $I_0$ ,  $I_2$  get selected at the 1st level, i.e., Input w/ 0 in LSB.

When  $S_0=1$ ,  $I_1$ ,  $I_3$  (LSB=1) get selected at the 1st level.

If  $S_0 = 0$ ,  $I_0$ ,  $I_2$ , become the 0th & 1st inputs to the next level.

At the next level, the I/P order # is determined by the rest of the bits of their index after stripping off the LSB.

Thus the design works as a 4:1 MUX.

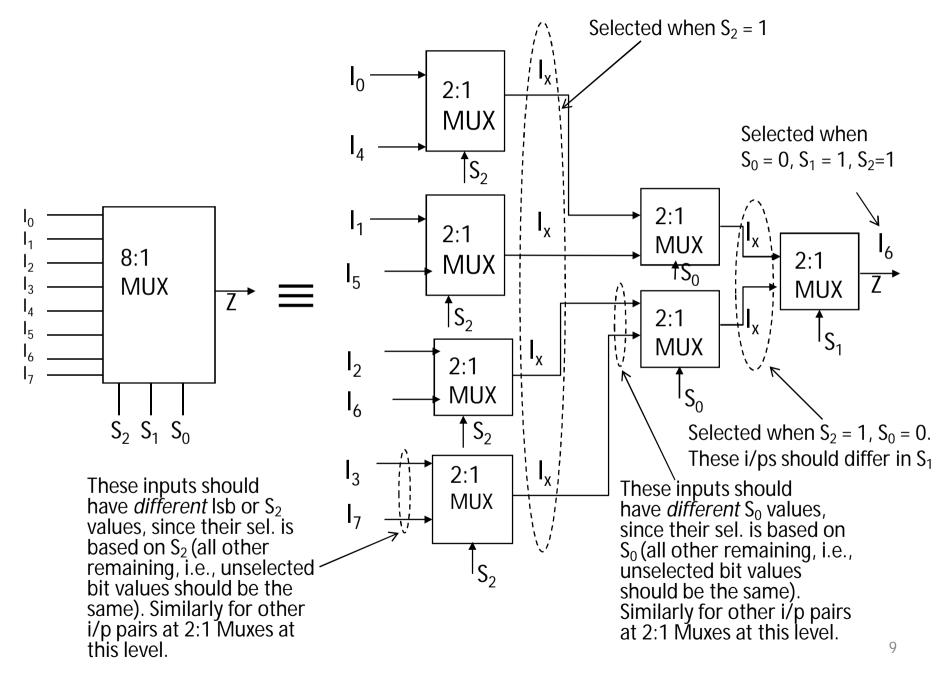

8:1 MUX's: Input groupings for a different control variable order

#### Non-Gate Logic

Introduction

AND-OR-Invert PAL/PLA Generalized Building Blocks Beyond Simple Gates

Kinds of "Non-gate logic":

- switching circuits built from CMOS transmission gates, ROMs

- multiplexer/selecter functions

- decoders

- tri-state and open collector gates

- read-only memories

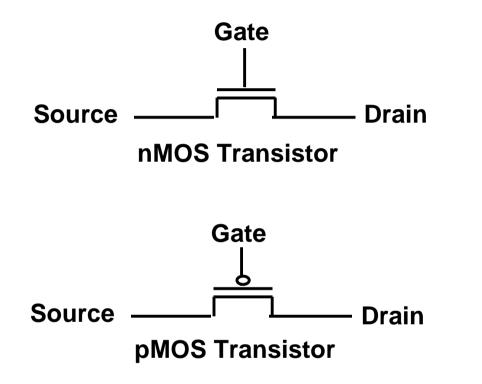

Voltage Controlled Switches

Logic 1 on gate, Source and Drain connected Normally open switch

Logic 0 on gate, Source and Drain connected Normally closed switch

**CMOS Transmission Gate**

nMOS transistors good at passing 0's but bad at passing 1's

pMOS transistors good at passing 1's but bad at passing 0's

perfect "transmission" gate places these in parallel:

Steering logic circuit – route data inputs to outputs based on the settings of control signals. Ex) selector fun or mux

Selection Function/Demultiplexer Function with Transmission Gates

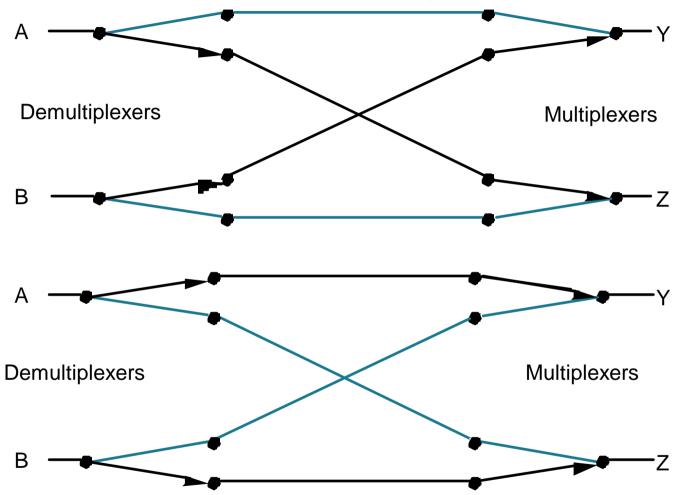

#### Use of Multiplexer/Demultiplexer in Digital Systems

So far, we've only seen point-to-point connections among gates

# Mux/Demux used to implement multiple source/multiple destination interconnect

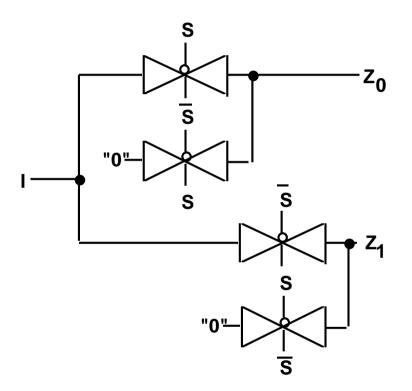

Well-formed Switching Networks

Problem with the Demux implementation: multiple outputs, but only one connected to the input!

The fix: additional logic to drive every output to a known value (steer '0' to Z0 or Z1) Never allow outputs to "float"

• State steering logic and discuss design of any combinational circuit using steering logic.