### VLSI DESIGN RULES

From Physical Design of CMOS

Integrated Circuits Using L-EDIT, John

P. Uyemura

# Minimum Width and spacing Rules

$\lambda = 1 \mu m$

#### MINIMUM WIDTH AND SPACING RULES

| LAYER   | TYPE OF RULE                     | VALUE    |

|---------|----------------------------------|----------|

| POLY    | Minimum Width<br>Minimum Spacing | 2λ<br>2λ |

| ACTIVE  | Minimum Width<br>Minimum Spacing | 3λ<br>3λ |

| NSELECT | Minimum Width<br>Minimum Spacing | 3λ<br>3λ |

| PSELECT | Minimum Width<br>Minimum Spacing | 3λ<br>3λ |

| METAL1  | Minimum Width<br>Minimum Spacing | 3λ<br>3λ |

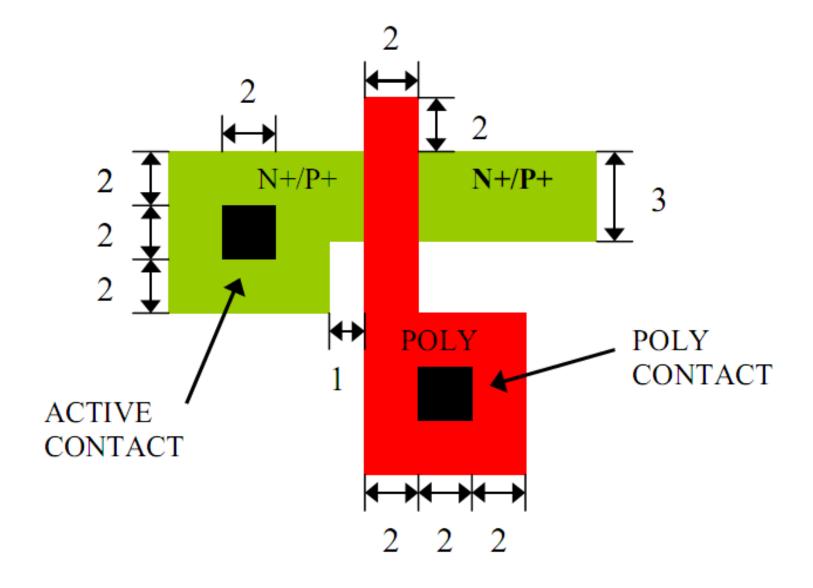

# **MOSFET Layout Rule**

| RULE           | MEANING                                    | VALUE         |

|----------------|--------------------------------------------|---------------|

| POLY Overlap   | Minimum extension over ACTIVE              | 2λ            |

| POLY-ACTIVE    | Minimum Spacing                            | 1λ            |

| MOSFET Width   | Minimum N+/P+ MOSFET W                     | 3λ            |

| ACTIVE CONTACT | Exact Size<br>Minimum Space to ACTIVE Edge | 2λ x 2λ<br>2λ |

| POLY CONTACT   | Exact Size<br>Minimum Space to POLY Edge   | 2λ x 2λ<br>2λ |

## Layout Design Rule