Introduction to CMOS VLSI Design

**CMOS Transistor Theory**

## pMOS I-V

- □ All dopings and voltages are inverted for pMOS

- $\hfill\square$  Mobility  $\mu_p$  is determined by holes

- Typically 2-3x lower than that of electrons  $\mu_n$

- 120 cm²/V\*s in AMI 0.6  $\mu m$  process

- □ Thus pMOS must be wider to provide same current

- In this class, assume  $\mu_n$  /  $\mu_p$  = 2

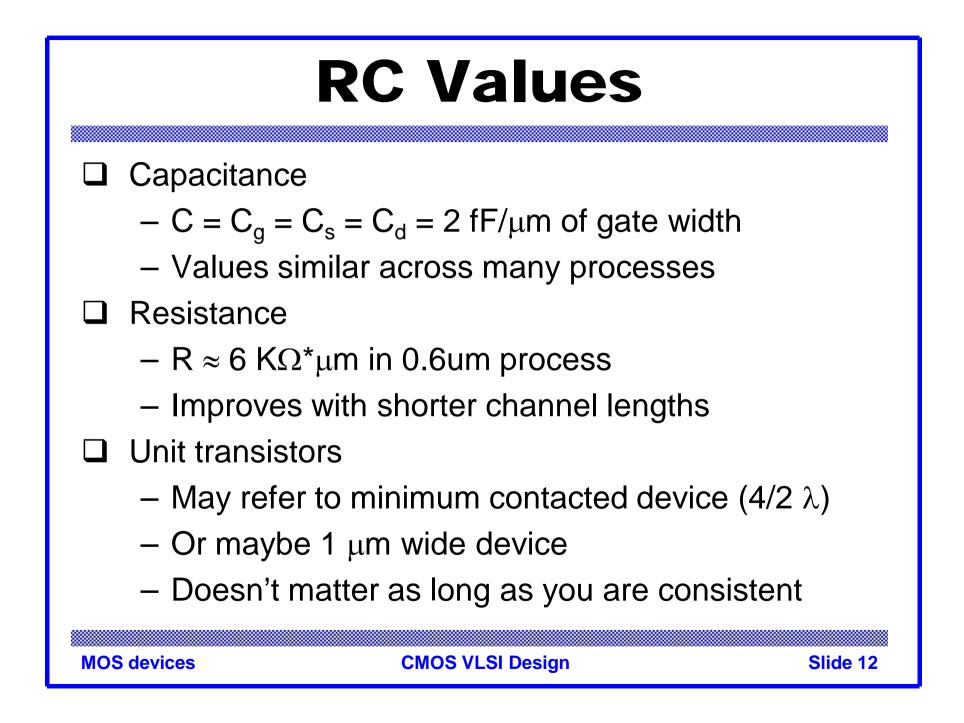

#### Capacitance

- Any two conductors separated by an insulator have capacitance

- Gate to channel capacitor is very important

- Creates channel charge necessary for operation

- Source and drain have capacitance to body

- Across reverse-biased diodes

- Called diffusion capacitance because it is associated with source/drain diffusion

### **Gate Capacitance**

# **Diffusion Capacitance**

- $\Box C_{sb}, C_{db}$

- ❑ Undesirable, called *parasitic* capacitance

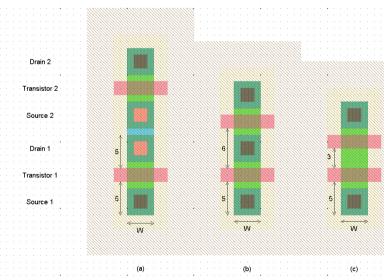

- Capacitance depends on area and perimeter

- Use small diffusion nodes

- Comparable to C<sub>g</sub>

for contacted diff

- $-\frac{1}{2}C_{g}$  for uncontacted

- Varies with process

**MOS devices**

**CMOS VLSI Design**

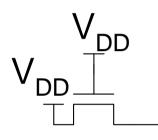

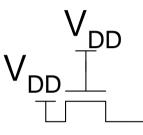

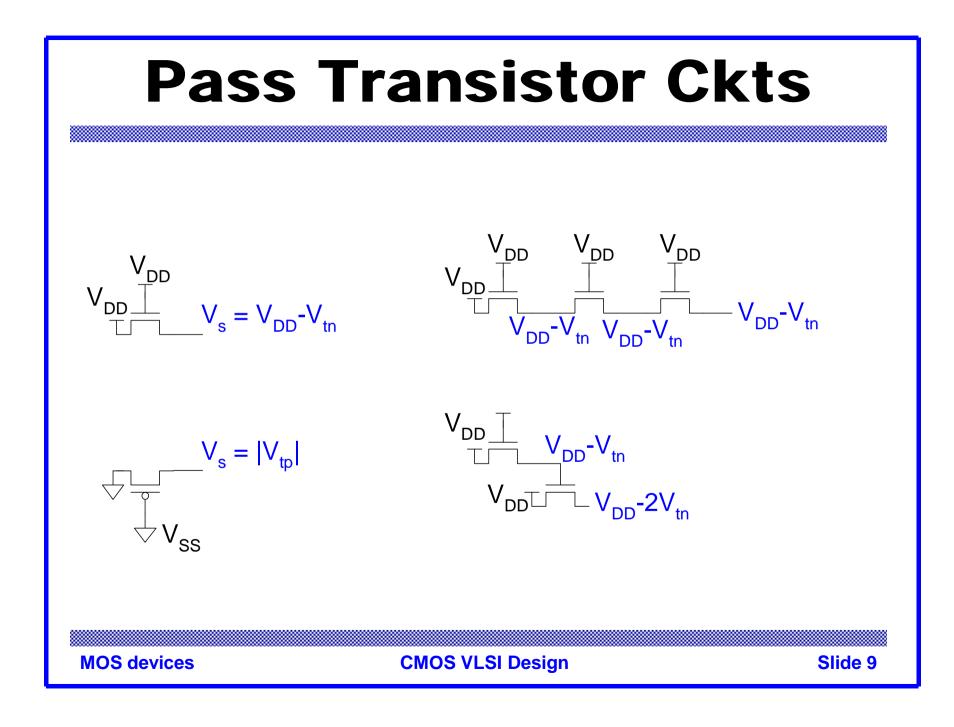

#### **Pass Transistors**

- We have assumed source is grounded

- ❑ What if source > 0?

- e.g. pass transistor passing V<sub>DD</sub>

### **Pass Transistors**

- **□**What if source > 0?

- e.g. pass transistor passing  $V_{\text{DD}}$

$$\Box$$

V<sub>g</sub> = V<sub>DD</sub>

$$- \text{ If } V_{\text{s}} > V_{\text{DD}} - V_{\text{t}}, V_{\text{gs}} < V_{\text{t}}$$

- Hence transistor would turn itself off

- □ nMOS pass transistors pull no higher than V<sub>DD</sub>-V<sub>tn</sub>

- Called a degraded "1"

- Approach degraded value slowly (low  $I_{ds}$ )

- pMOS pass transistors pull no lower than V<sub>tp</sub>

### **Effective Resistance**

- □ Shockley models have limited value

- Not accurate enough for modern transistors

- Too complicated for much hand analysis

- □ Simplification: treat transistor as resistor

- Replace  $I_{ds}(V_{ds}, V_{gs})$  with effective resistance R

- $I_{ds} = V_{ds}/R$

- R averaged across switching of digital gate

- □ Too inaccurate to predict current at any given time

- But good enough to predict RC delay

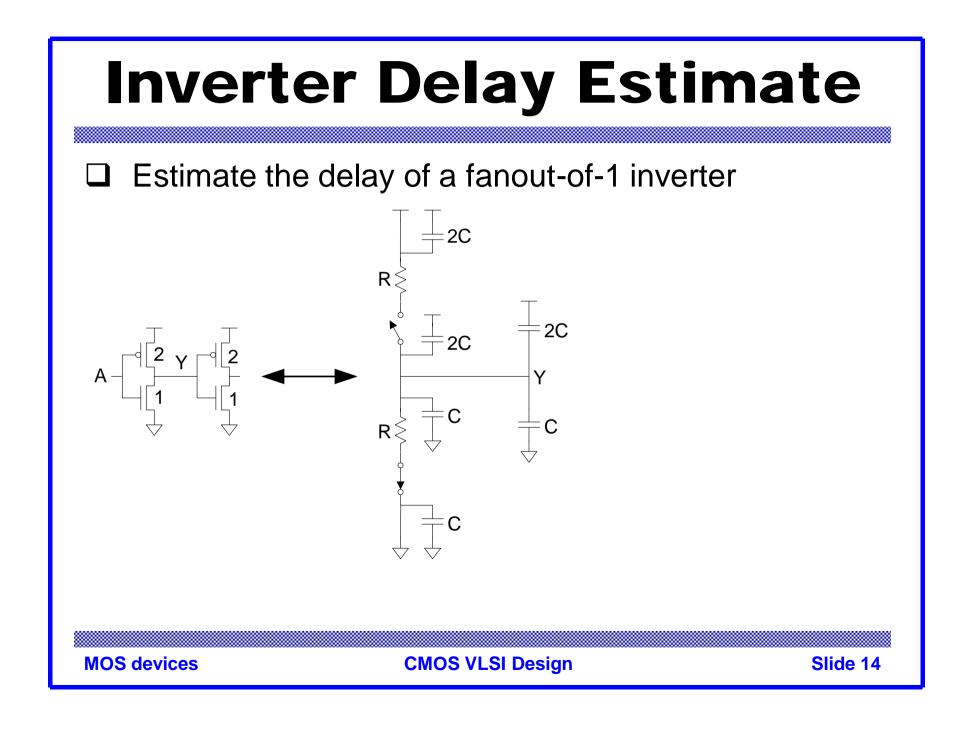

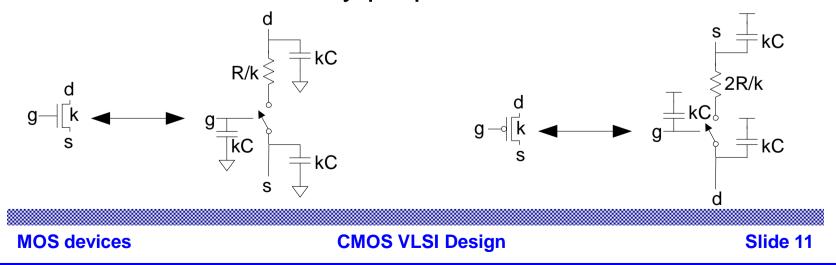

# **RC Delay Model**

- Use equivalent circuits for MOS transistors

- Ideal switch + capacitance and ON resistance

- Unit nMOS has resistance R, capacitance C

- Unit pMOS has resistance 2R, capacitance C

- Capacitance proportional to width

- Resistance inversely proportional to width

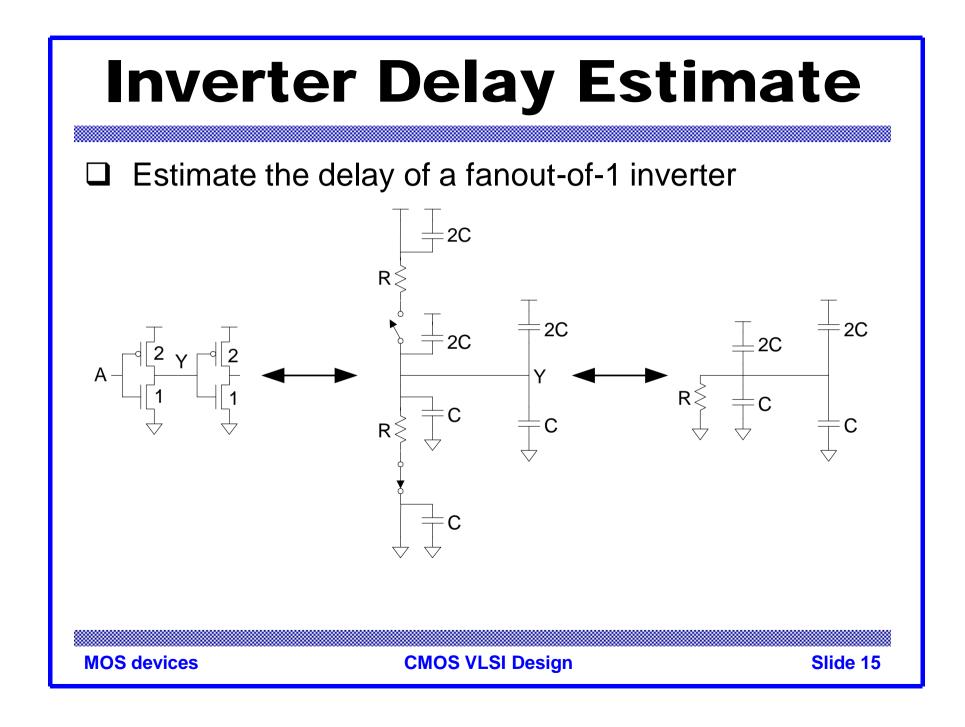

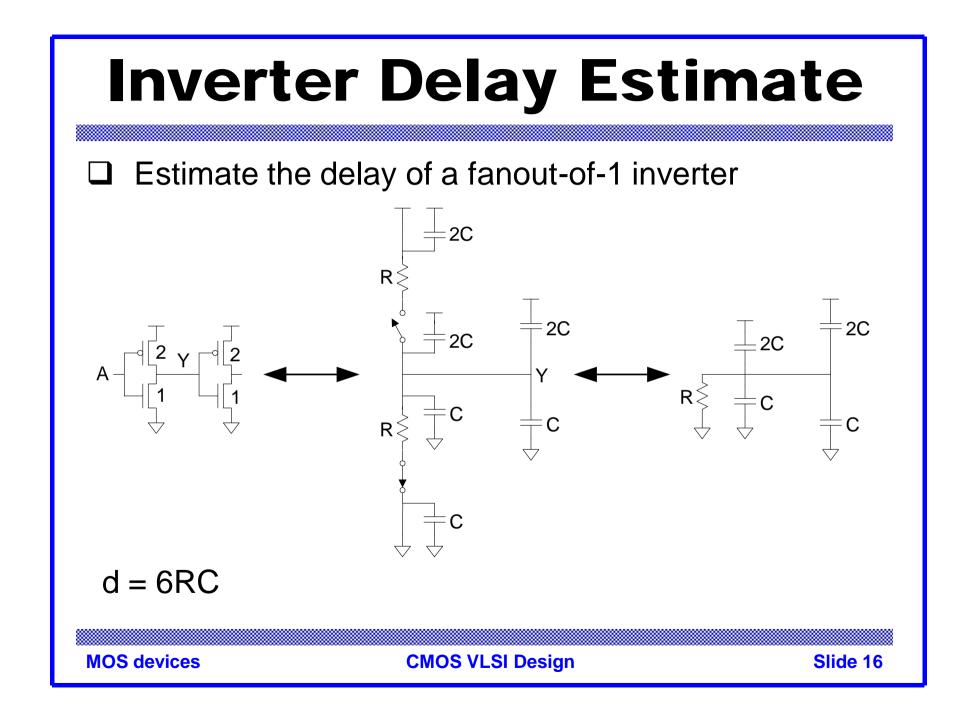

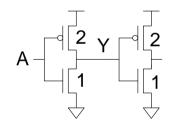

# **Inverter Delay Estimate**

□ Estimate the delay of a fanout-of-1 inverter

**MOS devices**

**CMOS VLSI Design**

Slide 13