# **ELECTRONICS DEVICES AND CIRCUITS SECTION - C TRANSISTORS**

## **OBJECTIVE**

# **MOSFETs**

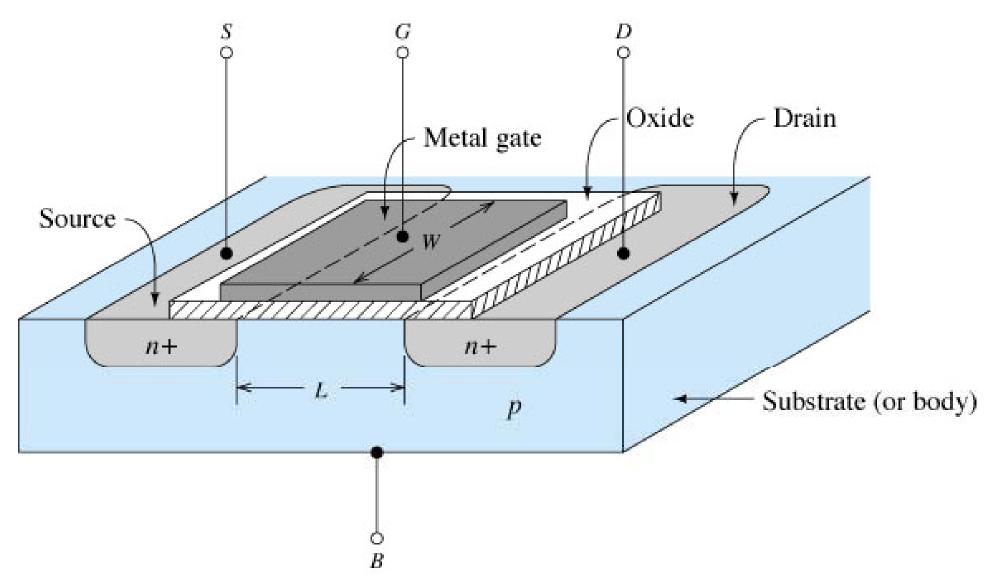

# n-Channel E-MOSFET showing channel length L and channel width W

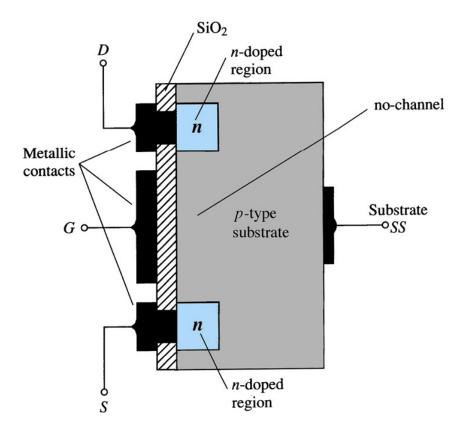

#### **Enhancement Mode MOSFET Construction**

The Drain (D) and Source (S) connect to the to n-doped regions

These n-doped regions are not connected via an n-channel without an

external voltage

The Gate (G) connects to the p-doped substrate via a thin insulating layer of SiO<sub>2</sub>

The n-doped material lies on a p-doped substrate that may have an additional terminal connection called SS

## **Specification Sheet**

#### MAXIMUM RATINGS

| Rating                                                                | Symbol          | Value       | Unit        |

|-----------------------------------------------------------------------|-----------------|-------------|-------------|

| Drain-Source Voltage                                                  | V <sub>DS</sub> | 25          | Vdc         |

| Drain-Gate Voltage                                                    | $V_{DG}$        | 30          | Vdc         |

| Gate-Source Voltage*                                                  | V <sub>GS</sub> | 30          | Vdc         |

| Drain Current                                                         | ID              | 30          | mAdc        |

| Total Device Dissipation @ T <sub>A</sub> = 25°C<br>Derate above 25°C | P <sub>D</sub>  | 300<br>1.7  | mW<br>mW/°C |

| Junction Temperature Range                                            | Tj              | 175         | *C          |

| Storage Temperature Range                                             | Tstg            | -65 to +175 | °C          |

#### ELECTRICAL CHARACTERISTICS (T<sub>A</sub> = 25°C unless otherwise noted.)

| Characteristic                                                                                                                 | Symbol               | Min  | Max      | Unit         |

|--------------------------------------------------------------------------------------------------------------------------------|----------------------|------|----------|--------------|

| OFF CHARACTERISTICS                                                                                                            |                      |      |          |              |

| Drain-Source Breakdown Voltage<br>$(I_D = 10 \mu A, V_{GS} = 0)$                                                               | V <sub>(BR)DSX</sub> | 25   | -        | Vdc          |

| Zero-Gate-Voltage Drain Current ( $V_{DS} = 10 \text{ V}, V_{OS} = 0$ ) $T_A = 25^{\circ}\text{C}$ $T_A = 150^{\circ}\text{C}$ | I <sub>DSS</sub>     | -    | 10<br>10 | nAdc<br>µAdc |

| Gate Reverse Current $(V_{GS} = \pm 15 \text{ Vdc}, V_{DS} = 0)$                                                               | I <sub>GSS</sub>     |      | ± 10     | pAdc         |

| ON CHARACTERISTICS                                                                                                             |                      |      |          |              |

| Gate Threshold Voltage $(V_{DS} = 10 \text{ V}, I_D = 10 \mu\text{A})$                                                         | V <sub>GS(Th)</sub>  | 1.0  | 5        | Vdc          |

| Drain-Source On-Voltage<br>( $I_D = 2.0 \text{ mA}, V_{GS} = 10V$ )                                                            | V <sub>DS(on)</sub>  | -    | 1.0      | v            |

| On-State Drain Current<br>(V <sub>GS</sub> = 10 V, V <sub>DS</sub> = 10 V)                                                     | I <sub>D(on)</sub>   | 3.0  | -        | mAdo         |

| SMALL-SIGNAL CHARACTERISTICS                                                                                                   |                      |      |          |              |

| Forward Transfer Admittance ( $V_{DS} = 10 \text{ V}, I_D = 2.0 \text{ mA}, f = 1.0 \text{ kHz}$ )                             | y <sub>fs</sub>      | 1000 | -        | μmho         |

| Input Capacitance $(V_{DS} = 10 \text{ V}, V_{QS} = 0, f = 140 \text{ kHz})$                                                   | C <sub>iss</sub>     | -    | 5.0      | pF           |

| Reverse Transfer Capacitance ( $V_{DS} = 0$ , $V_{OS} = 0$ , $f = 140$ kHz)                                                    | C <sub>rss</sub>     | 1    | 1.3      | pF           |

| Drain-Substrate Capacitance<br>(V <sub>D(SUB)</sub> = 10 V, f = 140 kHz)                                                       | C <sub>d(sub)</sub>  | -    | 5.0      | pF           |

| Drain-Source Resistance ( $V_{GS} = 10 \text{ V}, I_D = 0, f = 1.0 \text{ kHz}$ )                                              | f <sub>ds(on)</sub>  | -    | 300      | ohms         |

| SWITCHING CHARACTERISTICS                                                                                                      |                      |      |          |              |

| Turn-On Delay (Fig. 5)                                                                                                         | t <sub>d1</sub>      | -    | 45       | ns           |

| Rise Time (Fig. 6) $I_D = 2.0 \text{ mAdc}, V_{DS} = 10 \text{ Vdc},$                                                          | t <sub>r</sub>       | -    | 65       | ns           |

| Turn-Off Delay (Fig. 7) (V <sub>GS</sub> = 10 Vdc) (See Figure 9; Times Circuit Determined)                                    | t <sub>d2</sub>      | -    | 60       | ns           |

| Fall Time (Fig. 8)                                                                                                             | tr                   | _    | 100      | ns           |

<sup>\*</sup> Transient potentials of ± 75 Volt will not cause gate-exide failure.

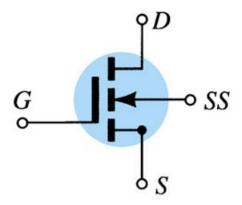

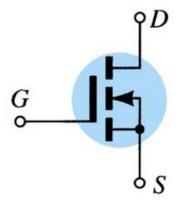

# **E-MOSFET Symbols**

#### *n*-channel

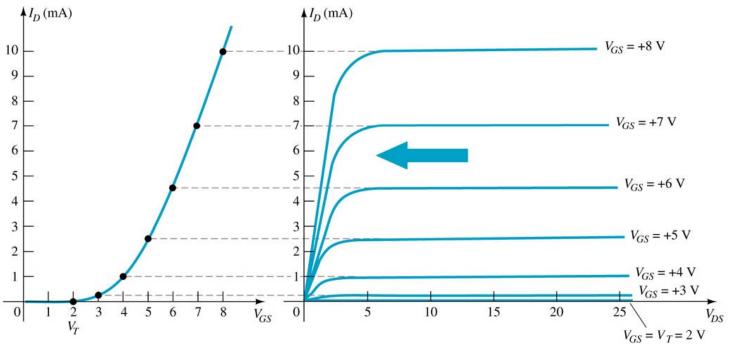

# **Basic Operation**

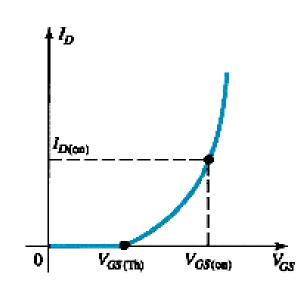

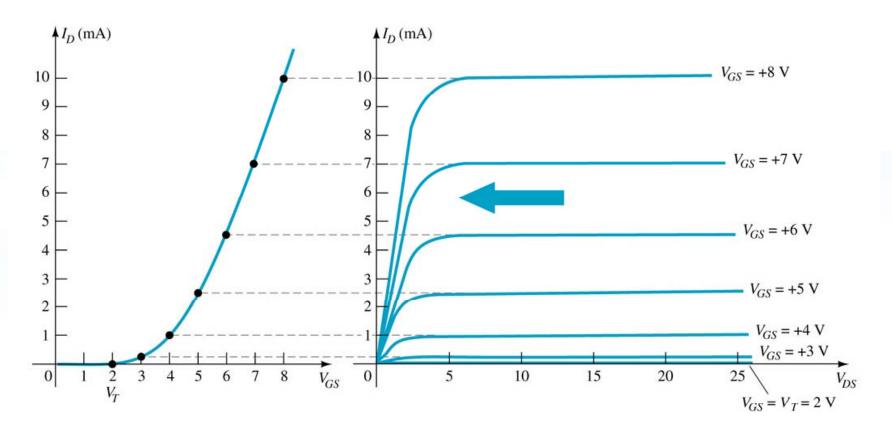

The Enhancement mode MOSFET only operates in the enhancement mode.

VGS is always positive

$I_{DSS} = 0$  when  $V_{GS} < V_{T}$

As VGS increases above VT, ID increases

If VGs is kept constant and VDs is increased, then ID saturates (IDSS)

The saturation level, VDSsat is reached.

#### **Transfer Curve**

To determine ID given VGS:  $I_D = k (V_{GS} - V_T)^2$  where  $V_T$  = threshold voltage or voltage at which the MOSFET turns on. k = constant found in the specification sheet

The P-Spice determination of k is based on the geometry of the device:  $\mathbf{k} = \mathbf{k}$

$$\mathbf{k} = \left(\frac{\mathbf{W}}{\mathbf{L}}\right) \left(\frac{\mathbf{KP}}{\mathbf{2}}\right)$$

where  $KP = \mu_N C_{OX}$

#### p-Channel Enhancement Mode MOSFETs

The p-channel Enhancement mode MOSFET is similar to the n-channel except that the voltage polarities and current directions are reversed.

# **Summary Table**

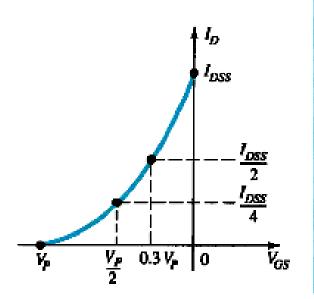

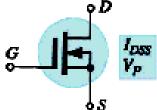

#### **JFET**

$$I_D = I_{DSS} \left( 1 - \frac{V_{GS}}{V_P} \right)^2$$

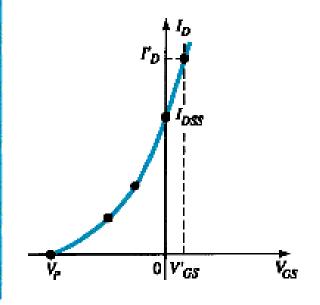

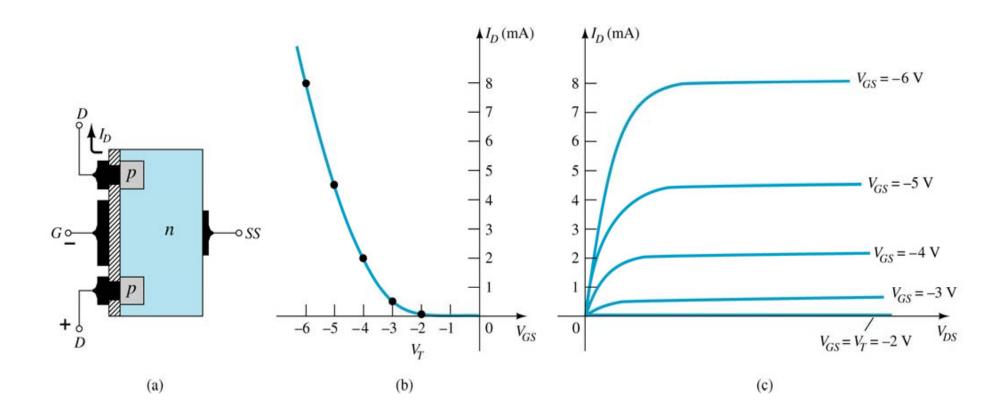

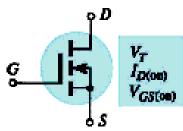

#### **D-MOSFET**

$$I_G = 0 \text{ A}, I_D = I_S$$

$$I_D = I_{DSS} \left( 1 - \frac{V_{GS}}{V_P} \right)^2$$

#### **E-MOSFET**

$$I_G = 0$$

A,  $I_D = I_S$

$$I_D = k (\frac{GS - V_{GS \text{ (Th)}})^2}{I_{D(\text{cen})}}$$

$$k = \frac{I_{D(\text{cen})}}{(V_{GS(\text{cen})} - V_{GS \text{ (Th)}})^2}$$