# **ELECTRONICS DEVICES AND CIRCUITS**

#### **SECTION - B**

# Semiconductors, Construction & Characteristics of Devices

# **OBJECTIVE**

# PLANAR TECHNOLOGY FOR DEVICE FABRICATION

### OUTLINE

- Introduction

- Why Silicon

- The purity of Silicon

- Czochralski growing process

- Fabrication processes

- Thermal

- Oxidation

- Etching techniques

- Oiffusion

# Expressions for diffusion of dopant, concentration

- Ion implantation

- Photomask generation

- Photolithography

- Epitaxial growth

- Metallization and interconnections,

- Ohmic contacts

- Planar PN junction diode fabrication,

- Fabrication of resistors and capacitors in IC's.

#### INTRODUCTION

- ➤The microminiaturization of electronics circuits and systems and then concomitant application to computers and communications represent major innovations of the twentieth century. These have led to the introduction of new applications that were not possible with discrete devices.

- Integrated circuits on a single silicon wafer followed by the increase of the size of the wafer to accommodate many more such circuits served to significantly reduce the costs while increasing the reliability of these circuits.

#### WHY SILICON?

#### Semiconductor devices are of two forms (i) Discrete Units

(ii) Integrated Units

Discrete Units can be diodes, transistors, etc.

Integrated Circuits uses these discrete units to make one device.

Integrated Circuits can be of two forms

(i) Monolithic-where transistors, diodes, resistors are fabricated and interconnected on the same chip.

(ii) Hybrid- in these circuits, elements are discrete form and others are connected on the chip with discrete elements externally to those formed on the chip

- Two other semiconductors, germanium and gallium arsenide, present special problems while silicon has certain specific advantages not available with the others.

- ✓ A major advantage of silicon, in addition to its abundant availability in the form of sand, is that it is possible to form a superior stable oxide, SiO<sub>2</sub>, which has superb insulating properties.

- ✓ Gallium arsenide crystals have a high density of crystal defects, which limit the performance of devices made from it.

- ✓Compound semiconductors, such as GaAs (in contrast to elemental semiconductors such as Si and Ge) are much more difficult to grow in single crystal form.

- ✓ Both Si and Ge do not suffer, in the processing steps, from possible decomposition that may occur in compound semiconductors such as GaAs.

- Lastly, at the present time, silicon remains the major semiconductor in the industry.

#### THE PURITY OF SILICON

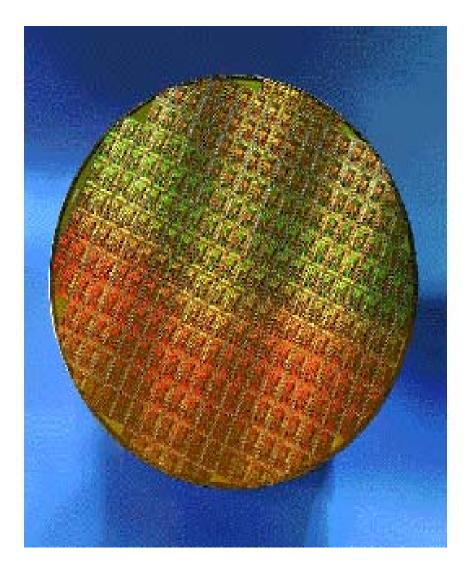

- The starting form of silicon, which manufacturers of devices and integrated circuits use, is a circular slice known as a *wafer*.

- These wafer diameters vary from 10-20 cms with maximum up to 30 cms.

- Silicon is found in abundance in nature as an oxide in sand and quartz.

- Silicon must be in

- ✓ Crystalline form,

- ✓ Very pure,

- ✓ Free of defects, and

- ✓ Uncontaminated.

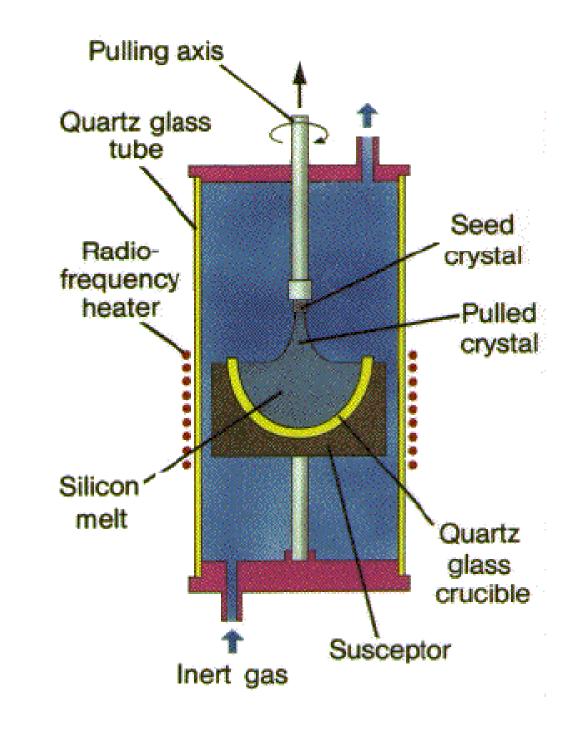

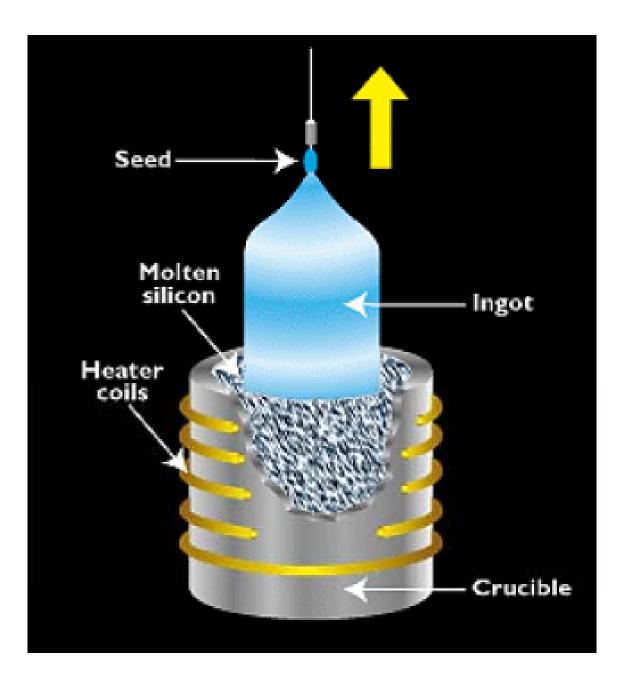

# The Czochralski Process

- To grow crystals, one starts with very pure semiconductor grade silicon, which is melted in a quartz-lined graphite crucible. The melt is held at a temperature of 1690K, which is slightly greater than the melting point (1685K) of silicon.

- A precisely controlled quantity of the dopant is added to the melt

The ratio of the concentration of impurities in the solid, C<sub>o</sub> to that in the liquid, C<sub>p</sub> is known as the equilibrium segregation coefficient k<sub>o</sub>

$k_o = C_o/C_l$

# Seed Crystal

After having set up the melt, a seed crystal (a small highly perfect crystal), attached to a holder and possessing the desired crystal orientation, is dipped into the melt and a small portion is allowed to melt.

#### Ingot Slicing and Wafer Preparation

- In the final process, when the bulk of the melt has been grown, the crystal diameter is decreased until there is a point contact with the melt.

- The resulting ingot is cooled and removed to be made into wafers. The ingots have diameters as large as 200mm, with latest ones approaching 300mm. The ingot length is of the order of 100cm.

- Slicing the wafers to be used in the fabrication of integrated circuits is a procedure that requires precision equipment.

- □ The object is to produce slices that are perfectly flat and as smooth as possible, with no damage to the crystal structure.

- The wafers need to be subjected to a number of steps known as lapping, polishing, and chemical etching.

- The wafers are cleaned, rinsed, and dried for use in the fabrication of discrete devices and integrated circuits

#### FABRICATION PROCESS

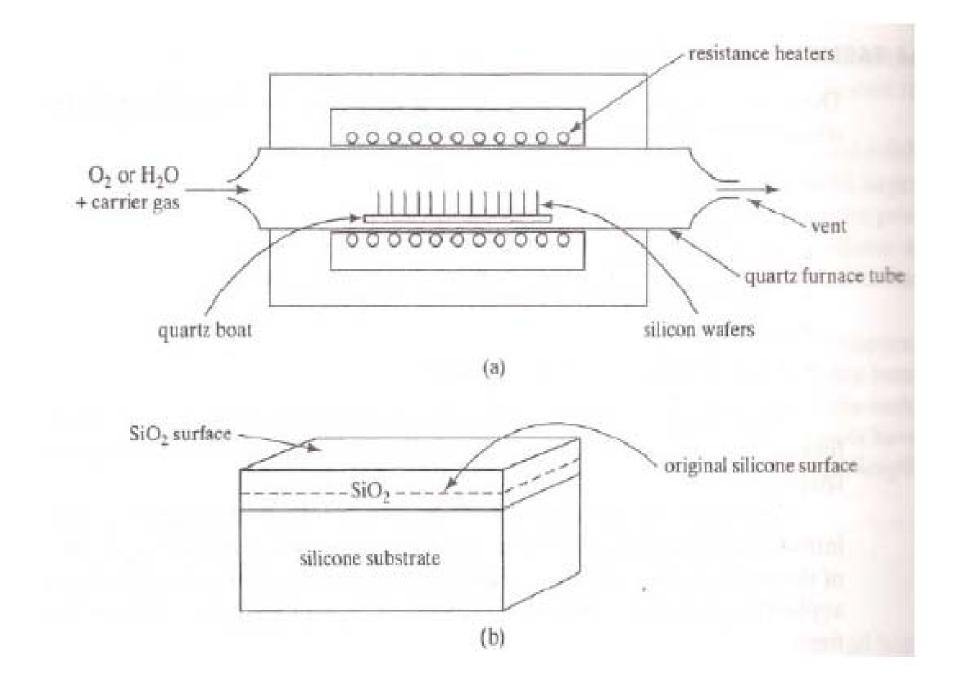

#### Oxidation

The process of oxidation consists of growing a thin film of silicon dioxide on the surface of the silicon wafer.

#### Diffusion

This process consists of the introduction of a few tenths to several micrometers of impurities by the solid-state diffusion of dopants into selected regions of a wafer to form junctions.

#### Ion Implantation

This is a process of introducing dopants into selected areas of the surface of the wafer by bombarding the surface with high-energy ions of the particular dopant.

#### Photolithography

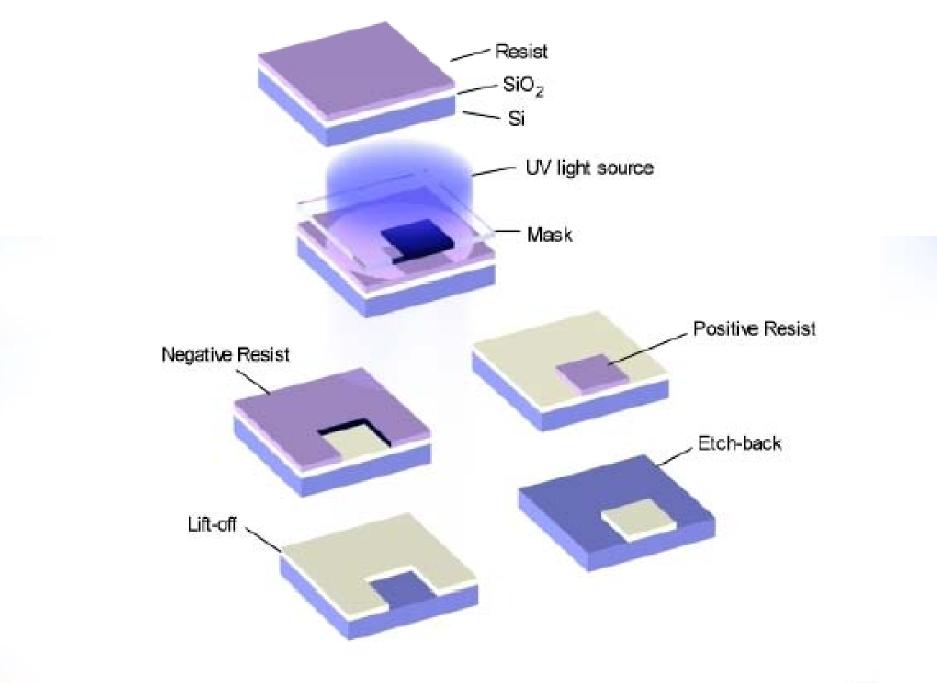

In this process, the image on the reticle is transferred to the surface of the wafer.

#### Epitaxy

Epitaxy is the process of the *controlled growth* of a crystalline doped layer of silicon on a single crystal substrate.

#### Metallization and interconnections

After all semiconductor fabrication steps of a device or of an integrated circuit are completed, it becomes necessary to provide metallic interconnections for the integrated circuit and for external connections to both the device and to the IC.

#### **Etching Techniques**

Etching is the process of selective removal of regions of a semiconductor, metal, or silicon dioxide.

There are two types of etchings: <u>wet</u> and <u>dry</u>

*In wet etching*, the wafers are immersed in a chemical solution at a predetermined temperature. In this process, the material to be etched is removed equally in all directions so that some material is etched from regions where it is to be left. This becomes a serious problem when dealing with small dimensions.

*In dry (or plasma) etching*, the wafers are immersed in a gaseous plasma created by a radio-frequency electric field applied to a gas such as argon. Electrons are initially released by field emission from an electrode. These electrodes gain kinetic energy from the field, collide with, and transfer energy to the gas molecules, which results in generating ions and electrons. The newly generated electrons collide with other gas molecules and the avalanche process continues throughout the gas, forming a plasma. The wafer to be etched is placed on an electrode and is subjected to the bombardment of its surface by gas ions. As a result, atoms at or near the surface to be etched are removed by the transfer of momentum from the ions to the atoms.

#### Diffusion

Most of these diffusion processes occur in two steps: the predeposition and the drive-in diffusion.

•In the pre deposition step, a high concentration of dopant atoms are introduced at the silicon surface by a vapor that contains the dopant at a temperature of about 1000°C. In recent years Ion Implantation is used.

•At the temperature of 1000°C, silicon atoms move out of their lattice sites creating a high density of vacancies and breaking the bond with the neighboring atoms.

The second step is drive in process, used to drive the impurities deeper into the surface without adding anymore impurities.

Common dopants are boron for P-type layers and phosphorus, antimony, and arsenic for N-type layers.

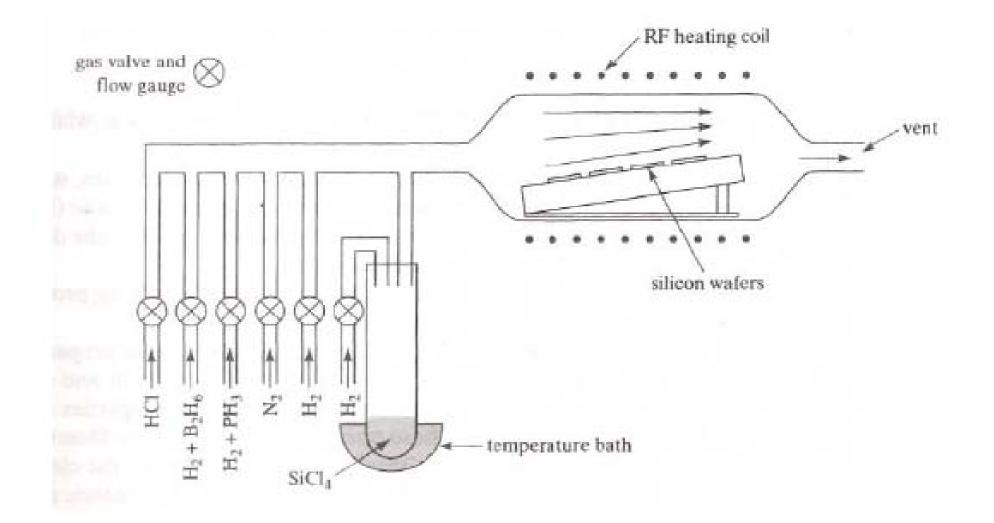

•A typical arrangement of the process of diffusion is shown in Figure.

•The wafers are placed in a quartz furnace tube that is heated by resistance heaters surrounding it. So that the wafers may be inserted and removed easily from the furnace, they are placed in a slotted quartz carrier known as a boat. To introduce a phosphorus dopant, as an example, phosphorus oxychloride

# Ion Implantation

To generate ions, such as those of phosphorus, an arc discharge is made to occur in a gas, such as phosphine (PH<sub>3</sub>), that contains the dopant.

The ions are then accelerated in an electric field so that they acquire an energy of about 20keV and are passed through a strong magnetic field.

Because during the arc discharge unwanted impurities may have been generated, the magnetic field acts to separate these impurities from the dopant ions based on the fact that the amount of deflection of a particle in a magnetic field depends on its mass.

Following the action of the magnetic field, the ions are further accelerated so that their energy reaches several hundred keV, whereupon they are focused on and strike the surface of the silicon wafer.

#### Photolithography

- 1. The wafer is baked at 100°C to solidify the resist on the wafer.

- 2. The reticle is placed on the wafer and aligned by computer control.

- The reticle is exposed to ultraviolet light with the transparent parts of the reticle passing the light onto the wafer. The photoresist under the opaque regions of the reticle is unaffected.

- The exposed photoresist is chemically removed by dissolving it in an organic solvent and exposing the silicon dioxide underneath. This is a process very similar to that used in developing photographic film.

- The exposed silicon dioxide is then etched away using hydrofluoric acid, which

- dissolves silicon dioxide and not silicon. The regions under the opaque part of

- the reticle are still covered by the silicon dioxide and the photoresist.

- The photoresist under the opaque regions of the reticle is stripped using a

- proper solvent and the silicon dioxide is exposed.

#### Epitaxial Growth

Epitaxy is used to deposit N on N+ silicon, which is impossible to accomplish by diffusion. It is also used in isolation between bipolar transistors wherein N- is deposited on P.

We list below, and with reference to Figure, the sequence of operation involved in the process:

1. Heat wafer to 1200°C.

2. Turn on H<sub>2</sub> to reduce the SiO<sub>2</sub> on the wafer surface.

3. Turn on anhydrous *HCl* to vapor-etch the surface of the wafer. This removes a small amount of silicon and other contaminants.

4. Turn off HCl.

- 5. Drop temperature to 1100°C.

- 6. Turn on silicon tetrachloride  $(SiCl_4)$ .

7. Introduce dopant.