# LECTURE 19

Microcontroller Performance

# Topics to be covered

PIC

To calculate the time any particular instruction will take to be executed, find the number of cycles, C, from the list in Appendix A. The time to execute that instruction is then found by multiplying C by 12 and dividing the product by the crystal frequency:

$$Tinst = \frac{C \times 12d}{crystal frequency}$$

For example, if the crystal frequency is 16 megahertz, then the time to execute an ADD A, R1 one-cycle instruction is .75 microseconds. A 12 megahertz crystal yields the convenient time of one microsecond per cycle. An 11.0592 megahertz crystal, while seemingly an odd value, yields a cycle frequency of 921.6 kilohertz, which can be divided evenly by the standard communication baud rates of 19200, 9600, 4800, 2400, 1200, and 300 hertz.

## PSW Program Status Word Register

| 7  | 6  | 5  | 4   | 3   | 2  | 1 | 0 |

|----|----|----|-----|-----|----|---|---|

| CY | AC | F0 | RS1 | RSO | ov | _ | P |

#### THE PROGRAM STATUS WORD (PSW) SPECIAL FUNCTION REGISTER

| Bit | Symbol | Function                                                               |             |                         |

|-----|--------|------------------------------------------------------------------------|-------------|-------------------------|

| 7   | CY     | Carry flag; used in arithmetic, JUMP, ROTATE, and BOOLEAN instructions |             |                         |

| 6   | AC     | Auxilliary carry flag; used for BCD arithmetic                         |             |                         |

| 5   | FO     | User flag 0                                                            |             |                         |

| 4   | RS1    | Register bank select bit 1                                             |             |                         |

| 3   | RSO    | Register bank select bit 0                                             |             |                         |

|     |        | RS1                                                                    | RS0         |                         |

|     |        | 0                                                                      | 0           | Select register bank 0  |

|     |        | 0                                                                      | 1           | Select register bank 1  |

|     |        | 1                                                                      | 0           | Select register bank 2  |

|     |        | 1                                                                      | 1           | Select register bank 3  |

| 2   | OV     | Overflow flag; used                                                    | in arithme  | tic instructions        |

| 1   | _      | Reserved for future use                                                |             |                         |

| 0   | Р      | Parity flag: shows pa                                                  | rity of rea | ister A: 1 = Odd Parity |

#### THE TIMER CONTROL (TCON) SPECIAL FUNCTION REGISTER

| Bit | Symbol | Function                                                                                                                                                                                                                                      |

|-----|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | TF1    | Timer 1 Overflow flag. Set when timer rolls from all ones to zero. Cleared when processor vectors to execute interrupt service routine located at program address 001Bh.                                                                      |

| 6   | TR1    | Timer 1 run control bit. Set to 1 by program to enable timer to count; cleared to 0 by program to halt timer. Does not reset timer.                                                                                                           |

| 5   | TFO    | Timer 0 Overflow flag. Set when timer rolls from all ones to zero. Cleared when processor vectors to execute interrupt service routine located at program address 000Bh.                                                                      |

| 4   | TRO    | Timer 0 run control bit. Set to 1 by program to enable timer to count; cleared to 0 by program to halt timer. Does not reset timer.                                                                                                           |

| 3   | IE1    | External interrupt 1 edge flag. Set to 1 when a high to low edge signal is received on port 3 pin 3.3 (INT1). Cleared when processor vectors to interrupt service routine located at program address 0013h. Not related to timer operations.  |

| 2   | IT1    | External interrupt 1 signal type control bit. Set to 1 by program to enable external interrupt 1 to be triggered by a falling edge signal. Set to 0 by program to enable a low level signal on external interrupt 1 to generate an interrupt. |

| 1   | IEO    | External interrupt 0 edge flag. Set to 1 when a high to low edge signal is received on port 3 pin 3.2 (INTO). Cleared when processor vectors to interrupt service routine located at program address 0003h. Not related to timer operations.  |

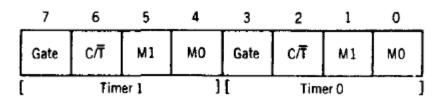

#### THE TIMER MODE CONTROL (TMOD) SPECIAL FUNCTION REGISTER

| Bit | Symbol | Function                                                                                                                                                                                                                                                         |

|-----|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7/3 | Gate   | OR gate enable bit which controls RUN/STOP of timer 1/0. Set to 1 by program to enable timer to run if bit TR1/0 in TCON is set and signal on external interrupt INT1/0 pin is high. Cleared to 0 by program to enable timer to run if bit TR1/0 in TCON is set. |

| 6/2 | c/ī    | Set to 1 by program to make timer 1/0 act as a counter by counting pulses from external input pins 3.5 (T1) or 3.4 (T0). Cleared to 0 by program to make timer act as a timer by counting internal frequency.                                                    |

| 5/1 | M1     | Timer/counter operating mode select bit 1. Set/cleared by program to select mode.                                                                                                                                                                                |

| 4/0 | M0     | Timer/counter operating mode select bit 0. Set/cleared by program to select mode.                                                                                                                                                                                |

|     |        | 144 140 14-d-                                                                                                                                                                                                                                                    |

| M1 | M0 | Mode |

|----|----|------|

| 0  | 0  | 0    |

| 0  | 1  | 1    |

| 1  | 0  | 2    |

| 1  | 1  | 3    |

### THE POWER MODE CONTROL (PCON) SPECIAL FUNCTION REGISTER

| Bit | Symbol. | Function                                                                                                                                                    |

|-----|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | SMOD    | Serial baud rate modify bit. Set to 1 by program to double baud rate using timer 1 for modes 1, 2, and 3. Cleared to 0 by program to use timer 1 baud rate. |

| 6-4 | _       | Not implemented.                                                                                                                                            |

| 3   | GF1     | General purpose user flag bit 1. Set/cleared by program.                                                                                                    |

| 2   | GF0     | General purpose user flag bit 0. Set/cleared by program.                                                                                                    |

| 1   | PD      | Power down bit. Set to 1 by program to enter power down configuration for CHMOS processors.                                                                 |

| 0   | IDŁ     | Idle mode bit. Set to 1 by program to enter idle mode configuration for CHMOS processors. PCON is not bit addressable.                                      |