# LECTURE 15, 16

**Internal Memory**

# Topics to be covered

Internal memory

# **Internal Data Memory**

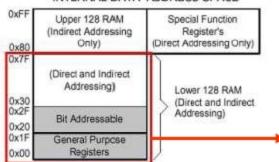

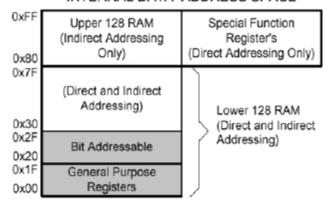

#### DATA MEMORY (RAM)

INTERNAL DATA ADDRESS SPACE

|   | Byte<br>Address | Bit Address                       |          |    |          |          |          |    |          |  |  |

|---|-----------------|-----------------------------------|----------|----|----------|----------|----------|----|----------|--|--|

| F | 7F              |                                   |          |    |          |          |          |    |          |  |  |

|   |                 | General<br>Purpose<br>RAM         |          |    |          |          |          |    |          |  |  |

| ŀ | 30              |                                   |          |    | -        |          |          |    | -        |  |  |

| ŀ | 2F              | 7F                                | 7E       | 70 | 70       | 7B       | 7A       | 79 | 78       |  |  |

| ŀ | 2E              | 77                                | 76       | 75 | 74       | 73       | 72       | 71 | 70       |  |  |

| 1 | 20              | 6F                                | 6E       | 60 | 6C       | 68       | BA       | 69 | 68       |  |  |

| ŀ | 20              | 67<br>5F                          | 66       | 66 | 64       | 63       | 52       | 61 | 60       |  |  |

| ŀ | 28              |                                   | 5E       | 50 | 5C       | 5B       | 5A       | 59 | 58       |  |  |

| ŀ | 2A<br>29        | 57<br>4F                          | 56<br>4E | 55 | 54<br>40 | 53<br>4B | 52<br>4A | 51 | 50<br>48 |  |  |

| ŀ | 28              | 47                                | 46       | 46 | 44       | 43       | 42       | 41 | 40       |  |  |

| ŀ | 27              | 3F                                | 3E       | 30 | 30       | 3B       | 3A       | 39 | 38       |  |  |

| ŀ | 26              | 37                                | 36       | 35 | 34       | 33       | 32       | 31 | 30       |  |  |

| ŀ | 25              | 2F                                | 2E       | 20 | 20       | 2B       | 2A       | 29 | 28       |  |  |

| ł | 24              | 27                                | 26       | 25 | 24       | 23       | 22       | 21 | 20       |  |  |

| ŀ | 23              | 1F                                | 1E       | 10 | 1C       | 1B       | 1A       | 19 | 18       |  |  |

| t | 22              | 17                                | 16       | 15 | 14       | 13       | 12       | 11 | 10       |  |  |

| t | 21              | OF                                | 0E       | 00 | oc       | OD       | DA       | 09 | 00       |  |  |

| Ì | 20              | 07                                | 06       | 05 | 04       | 03       | 02       | 01 | 00       |  |  |

| ı | 1F              |                                   |          |    |          |          |          |    |          |  |  |

| İ | 18              | Bank3                             |          |    |          |          |          |    |          |  |  |

| Ī | 17              | F-CROSSON                         |          |    |          |          |          |    |          |  |  |

| Ì | 10              | Bank 2                            |          |    |          |          |          |    |          |  |  |

| Ī | OF              |                                   |          |    | 15,000   | 10005    |          |    |          |  |  |

| İ | 08              | Pank 1                            |          |    |          |          |          |    |          |  |  |

| ľ | 07              |                                   |          |    |          |          |          |    |          |  |  |

| ľ | 00              | Default Register Bank for R0 - R7 |          |    |          |          |          |    |          |  |  |

# **Memory Organization**

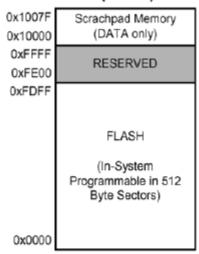

#### PROGRAM/DATA MEMORY (FLASH)

# DATA MEMORY (RAM) INTERNAL DATA ADDRESS SPACE

EXTERNAL DATA ADDRESS SPACE

- The memory organization of C8051F020 is similar to that of a standard 8051

- Program and data memory share the same address space but are accessed via different instruction types

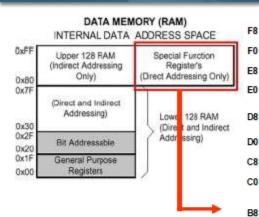

# **Special Function Registers**

| F8 | SPI0CN                     | PCA0H       | PCA0CPH0 | PCA0CPH1 | PCA0CPH2 | PCA0CPH3     | PCA0CPH4     | WDTCN   |

|----|----------------------------|-------------|----------|----------|----------|--------------|--------------|---------|

| F0 | В                          | SCOM        | SBUF1    | SADDR1   | TL4      | TH4          | EIP1         | EIP2    |

| E8 | ADC0CN                     | PCA0L       | PCA0CPL0 | PCA0CPL1 | PCA0CPL2 | PCA0CPL3     | PCA0CPL4     | RSTSRC  |

| E0 | ACC                        | XBR0        | XBR1     | XBR2     | RCAP4L   | RCAP4H       | EIE1         | EIE2    |

| D8 | PCA0CN                     | PCA0MD      | PCA0M0   | PCA0CPM1 | PCA0CPM2 | PCA0CPM<br>3 | PCA0CPM<br>4 |         |

| D0 | PSW                        | REF0CN      | DACOL    | DAC0H    | DAC0CN   | DAC1L        | DAC1H        | DAC1CN  |

| C8 | T2CON                      | T4CON       | RCAP2L   | RCAP2H   | TL2      | TH2          |              | SMB0CR  |

| C0 | SMB0CN                     | SMB0ST<br>A | SMB0DAT  | SMB0ADR  | ADC0GTL  | ADC0GTH      | ADC0LTL      | ADC0LTH |

| B8 | IP                         | SADEN0      | AMX0CF   | AMX0SL   | ADC0CF   | P1MDIN       | ADC0L        | ADC0H   |

| В0 | P3                         | OSCXCN      | OSCICN   |          |          | P74OUT       | FLSCL        | FLACL   |

| A8 | IE                         | SADDR0      | ADC1CN   | ADC1CF   | AMX1SL   | P3IF         | SADEN1       | EMI0CN  |

| A0 | P2                         | EMI0TC      |          | EMI0CF   | P0MDOUT  | P1MDOUT      | P2MDOUT      | P3MDOUT |

| 98 | SCON0                      | SBUF0       | SPI0CFG  | SPIODAT  | ADC1     | SPI0CKR      | CPT0CN       | CPT1CN  |

| 90 | P1                         | TMR3CN      | TMR3RLL  | TMR3RLH  | TMR3L    | TMR3H        | P7           |         |

| 88 | TCON                       | TMOD        | TL0      | TL1      | TH0      | TH1          | CKCON        | PSCTL   |

| 80 | P0                         | SP          | DPL      | DPH      | P4       | P5           | P6           | PCON    |

|    | 0(8)<br>Bit<br>addressable | 1(9)        | 2(A)     | 3(B)     | 4(C)     | 5(D)         | 6(E)         | 7(F)    |

# **Addressing Modes**

- Eight modes of addressing are available with the C8051F020

- The different addressing modes determine how the operand byte is selected

| Addressing Modes   | Instruction    |

|--------------------|----------------|

| Register           | MOV A, B       |

| Direct             | MOV 30H,A      |

| Indirect           | ADD A,@R0      |

| Immediate Constant | ADD A,#80H     |

| Relative*          | SJMP AHEAD     |

| Absolute*          | AJMP BACK      |

| Long*              | LJMP FAR_AHEAD |

| Indexed            | MOVC A,@A+PC   |

<sup>\*</sup> Related to program branching instructions

# **Register Addressing**

- The register addressing instruction involves information transfer between registers

- Example:

MOV RO, A

The instruction transfers the accumulator content into the R0 register. The register bank (Bank 0, 1, 2 or 3) must be specified prior to this instruction.

### **Direct Addressing**

This mode allows you to specify the operand by giving its actual memory address (typically specified in hexadecimal format) or by giving its abbreviated name (e.g. P3)

Note: Abbreviated SFR names are defined in the "C8051F020.inc" header file

Example:

```

MOV A, P3 ; Transfer the contents of ; Port 3 to the accumulator

MOV A, O2OH ; Transfer the contents of RAM ; location 20H to the accumulator

```

# **Indirect Addressing**

- This mode uses a pointer to hold the effective address of the operand

- Only registers R0, R1 and DPTR can be used as the pointer registers

- The R0 and R1 registers can hold an 8-bit address, whereas DPTR can hold a 16-bit address

#### Examples:

```

MOV @RO,A ;Store the content of ;accumulator into the memory ;location pointed to by ;register RO. RO could have an ;8-bit address, such as 60H.

MOVX A,@DPTR ;Transfer the contents from ;the memory location ;pointed to by DPTR into the ;accumulator. DPTR could have a ;16-bit address, such as 1234H.

```

### **Immediate Constant Addressing**

- This mode of addressing uses either an 8- or 16-bit constant value as the source operand

- This constant is specified in the instruction, rather than in a register or a memory location

- The destination register should hold the same data size which is specified by the source operand

- Examples:

```

ADD A,#030H ;Add 8-bit value of 30H to ;the accumulator register ;(which is an 8-bit register).

MOV DPTR,#0FE00H ;Move 16-bit data constant ;FE00H into the 16-bit Data ;Pointer Register.

```

### **Relative Addressing**

- This mode of addressing is used with some type of jump instructions, like SJMP (short jump) and conditional jumps like JNZ

- These instructions transfer control from one part of a program to another

- The destination address must be within -128 and +127 bytes from the current instruction address because an 8-bit offset is used (2<sup>8</sup> = 256)

- Example:

```

GoBack: DEC A ; Decrement A

```

JNZ GoBack ; If A is not zero, loop back

### **Absolute Addressing**

- Two instructions associated with this mode of addressing are ACALL and AJMP instructions

- These are 2-byte instructions where the 11-bit absolute address is specified as the operand

- The upper 5 bits of the 16-bit PC address are not modified. The lower 11 bits are loaded from this instruction. So, the branch address must be within the current 2K byte page of program memory (2<sup>11</sup> = 2048)

- Example:

```

ACALL PORT_INIT ; PORT_INIT should be ; located within 2k bytes.

```

PORT\_INIT: MOV PO, #OFH ; PORT\_INIT subroutine

### **Long Addressing**

- This mode of addressing is used with the LCALL and LJMP instructions

- It is a 3-byte instruction and the last 2 bytes specify a 16-bit destination location where the program branches

- It allows use of the full 64 K code space

- The program will always branch to the same location no matter where the program was previously

- Example:

```

LCALL TIMER_INIT ;TIMER_INIT address (16-bits ;long) is specified as the ;operand; In C, this will be a ;function call: Timer_Init().

TIMER_INIT: ORL TMOD,#01H ;TIMER_INIT subroutine

```

#### **Indexed Addressing**

- The Indexed addressing is useful when there is a need to retrieve data from a look-up table

- A 16-bit register (data pointer) holds the base address and the accumulator holds an 8-bit displacement or index value

- The sum of these two registers forms the effective address for a JMP or MOVC instruction

- Example:

After the execution of the above instructions, the program will branch to address 1F08H (1F00H+08H) and transfer into the accumulator the data byte retrieved from that location (from the look-up table)