# **LECTURE 23**

## **DIGITAL LOGIC FAMILIES**

#### **Primitive Flow Table**

Present StateNextStateOutput ZThe next1120Step is to draw the state table givingthe information

in tabular form<sub>2</sub>i.e. the primitive flow table

| 3 | 3 | 4 | 0 |

|---|---|---|---|

| 4 | 1 | 4 | 1 |

### **Flow Table**

- Stable states are again indicated by circles around the stable state numbers in the Next State columns

- **1**, 2, 3, 4

- Circled state will be the same as the number in the present state column.

- Output tries to attain to the stable state

- Primitive flow table should then be minimised where possible

- no minimisation in this example.

- Secondary variables are now assigned.

| Present<br>State | Ne<br>xt | Sta<br>te | Output<br>Z |

|------------------|----------|-----------|-------------|

| 1                | 1        | 2         | 0           |

| 2                | 3        | 2         | 0           |

| 3                | 3        | 4         | 0           |

| 4                | 1        | 4         | 1           |

#### **Assigning Secondary Variables**

- Care must be taken not to make an assignment, which results in more than one variable change between states.

- Use a transition table/map which has states chosen for each square on the map

Transitions from one state to another are marked on the map and if any show a diagonal path across two variable changes, a new assignment must be made.

#### **Assigning Secondary Variables**

The assigned flow table can then be written by inspection.

| Present State $y_1y_2$ | Next<br>0 | State Y <sub>1</sub> Y <sub>2</sub><br>1 | Output Z |

|------------------------|-----------|------------------------------------------|----------|

| 1                      | 00        | 01                                       | 0        |

| 2                      | 11        | 01                                       | 0        |

| 3                      | 11        | 10                                       | 0        |

| 4                      | 00        | 10                                       | 1        |

Swapping state assignments for 1 and 2 would result in an unsatisfactory map.

- Two principal implementations possible

- 1. Purely combinational logic gates

- 2. Combinational logic gates with asynchronous RS flip flops.

- Historically, asynchronous sequential circuits were known and used before synchronous sequential circuits were developed

- First practical digital systems were constructed with delays which were more adaptable to asynchronous type operations

- For this reason, the traditional method of asynchronous sequential circuit configuration has been with components that are connected to form one or more feedback loops.

- As electronic digital circuits were developed, it was realised that the flip-flop could be used as the memory element.

- Use of RS-latch in asynchronous sequential circuits produces a more orderly pattern, which may result in a reduction of the circuit complexity.

- An added advantage is that the circuit resembles the synchronous circuit in having distinct memory elements that store and specify the internal states.

- The RS-flip flip design approach assigns one flip-flop for each secondary variable.

- The inputs to these flip-flops are determined by the required change of y to Y.

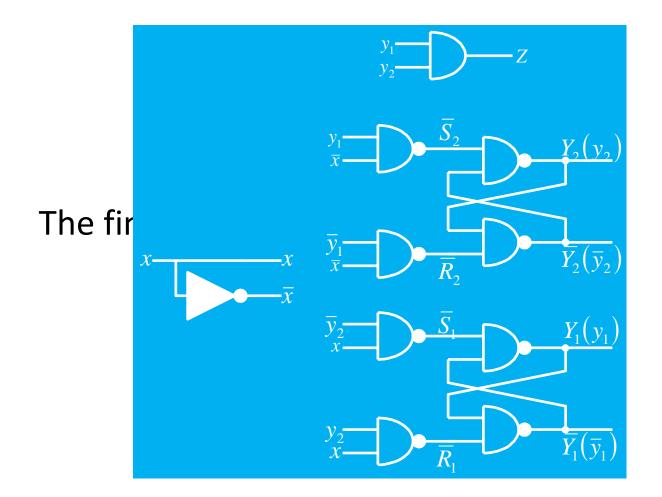

## **Circuit Implementation with RS Flipflops**

Using the following table

| Required<br>Change Q <sub>t</sub> | Output<br>To Q <sub>t+1</sub> | Flip-flop<br>S | Inputs<br>R |

|-----------------------------------|-------------------------------|----------------|-------------|

| 0                                 | 0                             | 0              | Х           |

| 0                                 | 1                             | 1              | 0           |

| 1                                 | 0                             | 0              | 1           |

| 1                                 | 1                             | Х              | 0           |

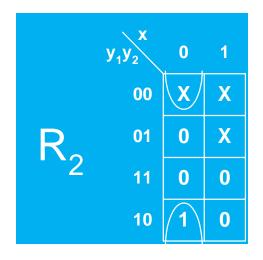

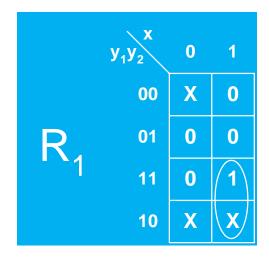

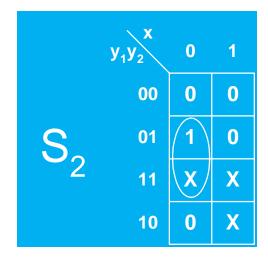

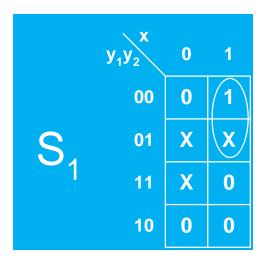

$\Rightarrow$  Obtain one function for each flip-flop input as shown below.

- A particular advantage of the RS flip-flop method is that it is not necessary to correct for static hazards

- As all the prime implicants are present in both the set and reset functions, which will be the case in all problems.

- Hence the RS flip-flop method often requires less components.

- In the RS flip-flop method, both true and complemented y outputs are available for feedback to the flip-flop inputs.

- If the set and reset function of the flip-flop includes true and complemented variables, it is possible that both Set and Reset are a 1 together during a transition, causing both the y and outputs to be 0.

- This might cause a critical race hazard, though this is unlikely with two-level circuits. The inverse y and output can be generates using a separate gate is necessary.