CAO: Lecture 6 Sequential logic blocks (Latches, Flip-Flops, Registers, Counters)

# **Topics Covered**

- Overview

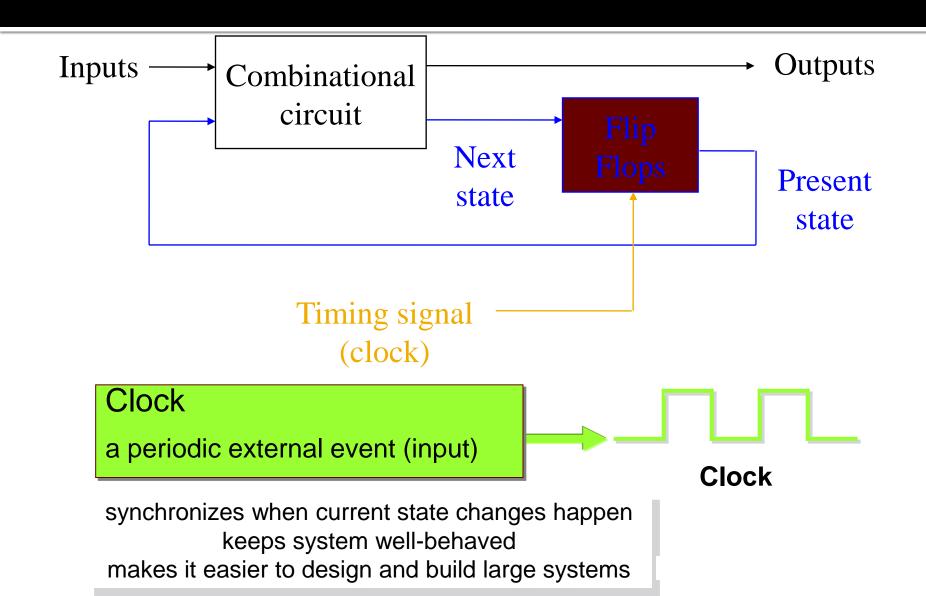

- Sequential Circuits

- Cross-coupled Inverters

- S-R Latch with NORs

- S-R Latch with NANDs

- D Latch

- Symbols for Latches

# Overview

- Circuits require memory to store intermediate data

- Sequential circuits use a periodic signal to determine when to store values.

- A clock signal can determine storage times

- Clock signals are periodic

- Single bit storage element is a flip flop

- A basic type of flip flop is a latch

- Latches are made from logic gates

- NAND, NOR, AND, OR, Inverter

# The story so far ...

- Logical operations which respond to combinations of inputs to produce an output.

- Call these combinational logic circuits.

- For example, can add two numbers. But:

- No way of adding two numbers, then adding a third (a sequential operation);

- No way of remembering or storing information after inputs have been removed.

- To handle this, we need sequential logic capable of storing intermediate (and final) results.

# **Sequential Circuits**

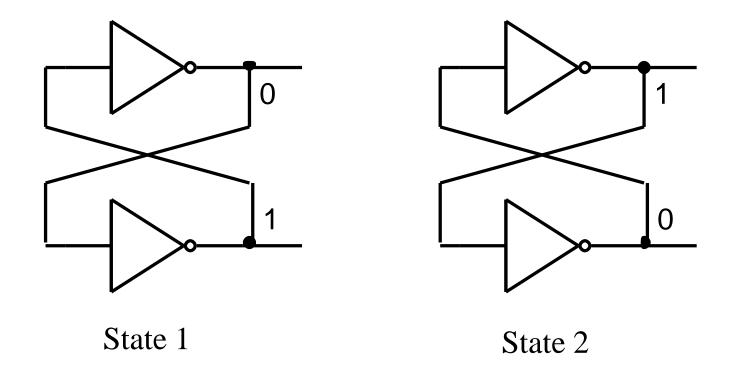

# **Cross-coupled Inverters**

° A stable value can be stored at inverter outputs

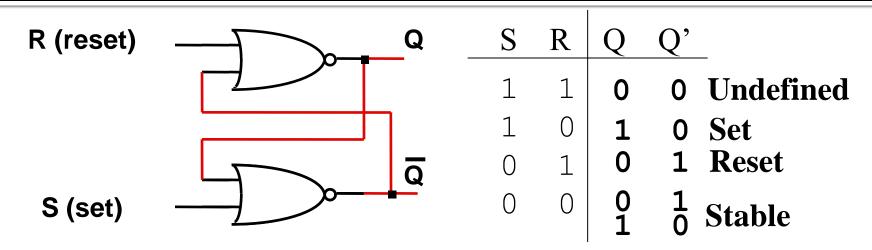

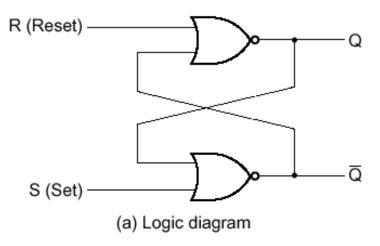

# S-R Latch with NORs

- S-R latch made from cross-coupled NORs

- If Q = 1, set state

- If Q = 0, reset state

- Usually S=0 and R=0

- S=1 and R=1 generates unpredictable results

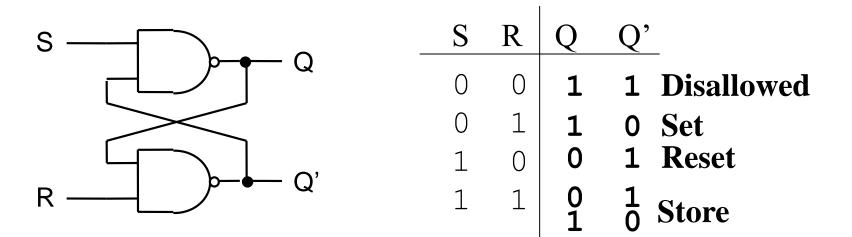

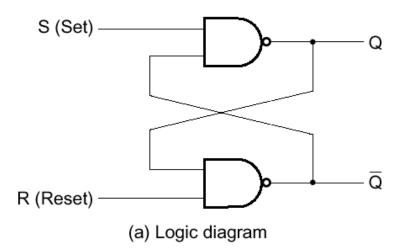

# S-R Latch with NANDs

- Latch made from cross-coupled NANDs

- Sometimes called S'-R' latch

- Usually S=1 and R=1

- S=0 and R=0 generates unpredictable results

#### S-R Latches

| S | R | Q | Q |             |

|---|---|---|---|-------------|

| 1 | 0 | 1 | 0 | Set state   |

| 0 | 0 | 1 | 0 | Sel slale   |

| 0 | 1 | 0 | 1 |             |

| 0 | 0 | 0 | 1 | Reset state |

| 1 | 1 | 0 | 0 | Undefined   |

|   |   |   |   |             |

(b) Function table

| S | R | Q | Q |             |

|---|---|---|---|-------------|

| 0 | 1 | 1 | 0 | Cot ototo   |

| 1 | 1 | 1 | 0 | Set state   |

| 1 | 0 | 0 | 1 |             |

| 1 | 1 | 0 | 1 | Reset state |

| 0 | 0 | 1 | 1 | Undefined   |

(b) Function table

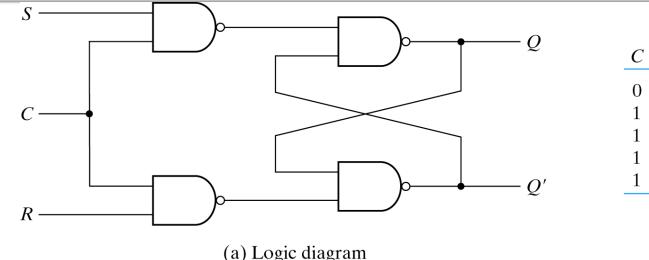

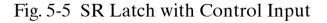

# S-R Latch with control input

| С                | S                | R                | Next state of $Q$                                                                 |

|------------------|------------------|------------------|-----------------------------------------------------------------------------------|

| 0<br>1<br>1<br>1 | X<br>0<br>0<br>1 | X<br>0<br>1<br>0 | No change<br>No change<br>Q = 0; Reset state<br>Q = 1; set state<br>Indeterminate |

(b) Function table

- Occasionally, desirable to avoid latch changes

- C = 0 disables all latch state changes

- Control signal enables data change when C = 1

- ° Right side of circuit same as ordinary S-R latch.

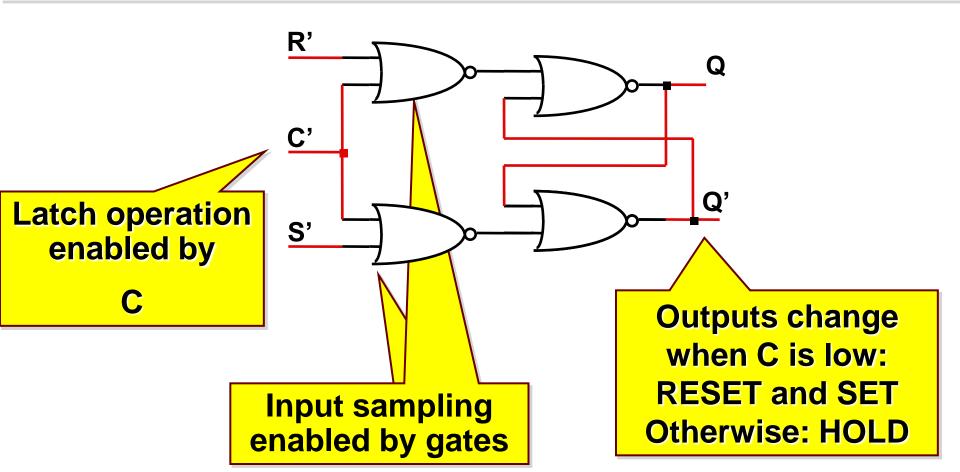

# NOR S-R Latch with Control Input

### Latch is level-sensitive, in regards to C

### Only stores data if C' = 0

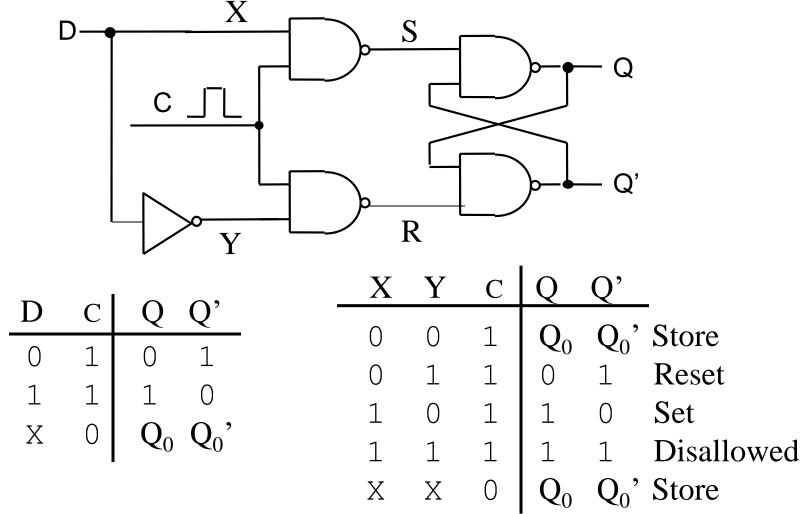

# **D** Latch

° Q<sub>0</sub> indicates the previous state (the previously stored value)

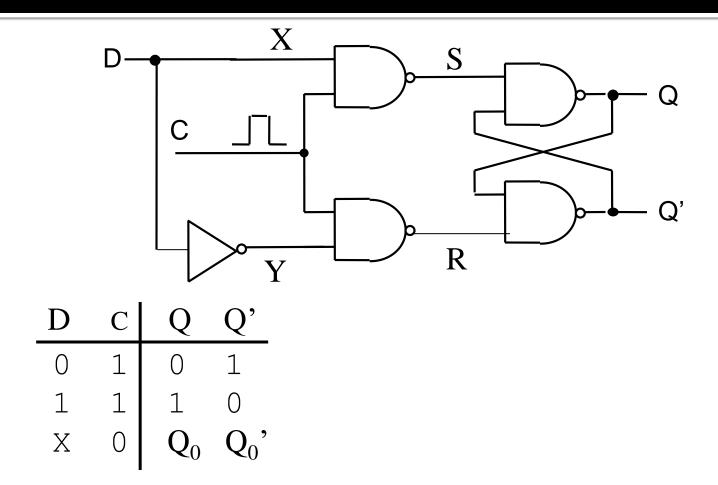

# **D** Latch

- Input value D is passed to output Q when C is high

- <sup>°</sup> Input value **D** is ignored when **C** is low

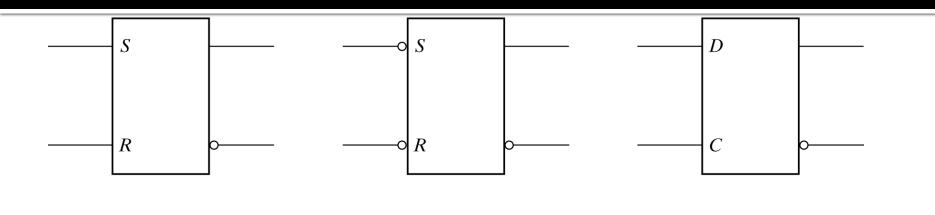

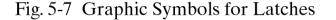

# **Symbols for Latches**

SR

D

- SR latch is based on NOR gates

- S'R' latch based on NAND gates

- <sup>°</sup> D latch can be based on either.

- <sup>°</sup> D latch sometimes called transparent latch

# Summary

- Latches are based on combinational gates (e.g. NAND, NOR)

- Latches store data even after data input has been removed

- S-R latches operate like cross-coupled inverters with control inputs (S = set, R = reset)

- With additional gates, an S-R latch can be converted to a D latch (D stands for data)

- D latch is simple to understand conceptually

- When C = 1, data input D stored in latch and output as Q

- When C = o, data input D ignored and previous latch value output at Q

- Next time: more storage elements!